Операционный автомат для умножения двоичных чисел

Допустимы пути, содержащие несколько условных вершин или не содержащие ни одной, а также пути, не имеющие операторной вершины. Рассматриваются все пути, кроме тех, в которых некоторое условие входит как в прямой, так и в инверсной форме. Множество путей (1) определяет множество переходов между состояниями и автомата. При построении графа переходов каждой отметке на граф-схеме алгоритма или… Читать ещё >

Операционный автомат для умножения двоичных чисел (реферат, курсовая, диплом, контрольная)

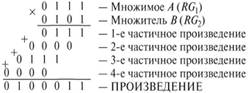

Для обоснования принципа построения операционного автомата воспользуемся правилом умножения двоичных чисел, при котором частичные произведения формируются, начиная с младших разрядов множителя В (рис. 5.3).

Выбор аппаратных средств для реализации операции умножения двоичных чисел. Прежде всего, необходимо иметь в виду, что суммирование частичных произведений должно осуществляться последовательно во времени с помощью сумматоров, предназначенных для сложения двух операндов, поскольку сложность схемного решения сумматоров возрастает как с ростом числа операндов, так и с увеличением их разрядности. Как видно из рисунка, особенность умножения двоичных чисел состоит в том, что частичные произведения могут принимать лишь два значения: значение множимого А либо значение нуля. Значение частичного произведения определяется значением текущего разряда множителя В. Если.

Рис. 5.3. Правило умножения двоичных чисел, начиная с младших разрядов множителя.

частичное произведение равно нулю, то микрооперацию сложения можно не выполнять. Таким образом, множимое А используется как частичное произведение, и его будем постоянно хранить в регистре RG1. Для аппаратного определения значения текущего разряда множителя Я необходимо располагать сдвигающим регистром RG2. В исходном состоянии регистр RG2 загружен множителем B, причем выходной сигнал должен соответствовать самому младшему разряду множителя. Чтобы выявить значение следующего разряда множителя В, после каждой микрооперации сложения частичного произведения необходимо производить сдвиг содержимого RG2 в сторону самого младшего разряда. Для хранения частичных сумм частичных произведений необходимо располагать третьим регистром RG3 В исходном состоянии RG3 должен быть загружен нулями. В процессе умножения осуществляется сложение содержимого регистра RG3 с частичным произведением А. Частичная сумма помещается в RG3, после чего выполняется сдвиг в сторону младших разрядов. При этом в два раза увеличивается вес каждого очередного разряда множителя В.

Алгоритм умножения двоичных чисел. На рис. 5.4 показан процесс умножения с использованием трех регистров и сумматора. Множимое А = 0111 постоянно находится в регистре RG1. В исходном состоянии в регистр RG3 помещен нуль 0000, а в регистр RG2 - множитель B=0101. Нуль в старшем разряде операндов A и Освидетельствует о том, что перемножаются положительные числа. В процессе умножения в регистре RG3 размещаются частичные суммы частичных произведений и произведение. Анализируется младший разряд регистра RG2 (МР RG2), который отождествляется с логическим условием Ху. Если МР RG2 = Х1 = 1, то выполняется микрооперация сложения содержимого регистров RG3 и RG1, и результат помещается в RG3. Эта микрооперация может быть записана в следующем виде: RG3: = RG3 + RG1. Затем осуществляется микрооперация сдвига вправо на один разряд (R1) содержимого составного регистра, образованного из регистров RG13 и RG2: RG13, RG2:=R1(RG3, RG2). Если же МР RG2 = Х1= 0, то выполняется только сдвиг содержимого составного регистра.

Из рис. 5.4 видно, что процесс носит циклический характер. Число циклов п равно числу разрядов множителя А (в примере п =4). По;

Рис. 5.4. Иллюстрация алгоритма умножения двоичных чисел с помощью трех регистров и сумматора.

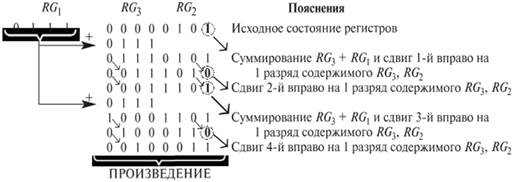

этому при схемной реализации для автоматической фиксации завершения операции умножения целесообразно использовать вычитающий счетчик СТ числа повторений цикла. В исходном состоянии счетчик загружается числом п = 4 (100). По завершении каждого цикла содержимое счетчика уменьшается на единицу. После 4-го цикла счетчик будет пуст (000). Если к выходам счетчика подключить логический элемент 3ИЛИ-НЕ и его выходной сигнал принять в качестве логического условия Х2, то Х2 = 1 будет свидетельствовать о завершении 4-го цикла или об окончании операции умножения.

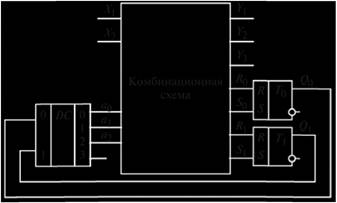

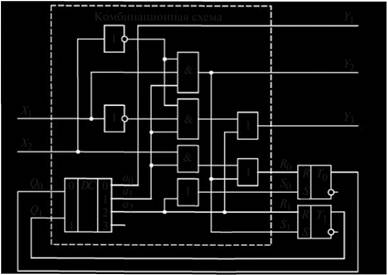

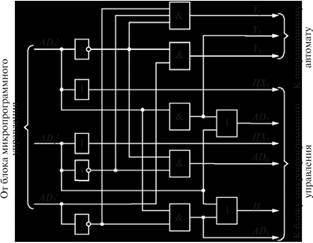

Структурная схема операционного автомата. Схема автомата для умножения двоичных чисел приведена на рис. 5.5. Составной регистр из RG$ и RG2 образован путем соединения выхода триггера младшего разряда RG$ с входом триггера старшего разряда RG2. С помощью управляющего сигнала y1 регистр RG$ устанавливается в нулевое состояние, а с помощью сигнала y2 в счетчик СТ вводится число п = 4. По команде у3 результаты суммирования содержимого RG$ и RG1 с выхода сумматора поступают в RG3. Для сдвига содержимого составного регистра RG3, RG2 используется управляющий сигнал y4, а для уменьшения показаний счетчика СТ на единицу — сигнал у5. Предполагается, что операнды А и В уже загружены в регистры. Управляющие сигналы y1| + у5 будем отождествлять с микрооперациями.

В операционном автомате формируются следующие признаки:

- • X1 — значение младшего разряда RG2. Значение Х1 = 1 свидетельствует о том, что младший разряд регистра RG2 равен 1. В этом случае выполняется описанная выше микрооперация сложения, а затем сдвига. При X1 = 0 младший разряд регистра RG2 равен 0 и выполняется только микрооперация сдвига;

- • Х2 - результат проверки на нуль содержимого СТ. Значение Х2 = 1 свидетельствует о том, что счетчик пуст (СТ = 000). В этом случае

Рис. 5.5. Структурная схема операционного аппарата для умножения двоичных чисел:

y1 — микрооперация загрузки регистра RG3 нулем; у2 - микрооперация загрузки счетчика СТ числом п = 4 (код 0100); у2 — микрооперация сложения содержимого регистров RG3, RG1 и загрузки результата в регистр RG3, у4 - микрооперация сдвига на один разряд вправо содержимого регистров RG3, RG2; у5 — микрооперация уменьшения на единицу содержимого счетчика СТ операция умножения завершается. При = 0 начинается новый цикл операции умножения.

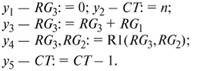

Приведем в условной записи список микроопераций, выполняемых в узлах операционного автомата, и список формируемых признаков:

Список микроопераций. | Список признаков. |

|  |

Управляющий автомат со схемной логикой. Рассмотрим основные этапы построения такого автомата.

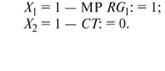

Построение граф-схемы алгоритма операции умножения. Граф-схема алгоритма представляет собой связанный граф со следующими основными типами вершин: начальная, конечная у операторная и условная. При составлении графа руководствуются следующими правилами:

- • граф-схема алгоритма должна содержать одну начальную, одну конечную вершины, а также конечное число операторных и условных вершин;

- • входы и выходы различных вершин соединяются дугами, направленными от выхода к входу. При этом выход каждой вершины соединяется только с одним входом;

- • в каждой операторной вершине записывается микрокоманда, представляющая собой набор микроопераций, выполняемых на одном временном интервале (такте);

- • в каждой условной вершине записывается одно bp логических условий;

- • между любой вершиной и конечной вершиной должен существовать по крайней мере один путь.

На основании приведенного выше списка микроопераций можно сформировать набор микрокоманд. Для этого необходимо:

- • объединить микрооперации y1, у2 (загрузки регистра RG3 и счетчика СТ) в общую микрокоманду Y1. = {y1, y2} так как они могут быть выполнены одновременно (на одном тактовом интервале);

- • выделить в отдельную микрокоманду микрооперацию сложения содержимого регистров RG3, + RG1 с загрузкой суммы в RG3 — Y2: =у3,

- • объединить микрооперации у4, у5 (сдвига вправо на один разряд содержимого регистровой пары RG3, RG2 и уменьшения на единицу содержимого счетчика СТ) в микрокоманду Y3: = {у4,у5}.

Для операции умножения можно построить несколько граф-схем, каждая из которых определяет свою структуру управляющего автомата и последовательность его функционирования. На рис. 5.6 приведен один из возможных вариантов граф-схемы алгоритма операции умножения двоичных чисел.

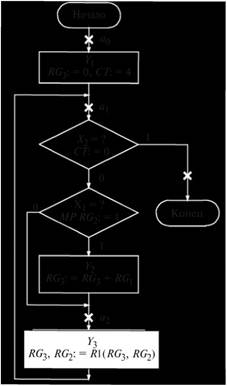

Построение графа переходов управляющего авто м, а т а. Г раф строится в два этапа. На первом этапе производится разметка граф-схемы алгоритма по следующим правилам:

- • символом a0 отмечается вход первой вершины, следующей за начальной, а также вход конечной вершины;

- • входы вершин, следующих за операторными вершинами, отмечаются символами a, a2, …;

- • входы двух различных вершин, за исключением конечной, не могут быть обозначены одинаковыми символами;

- • вход вершины может отмечаться только одним символом.

Отметки графа нанесены на рисунке в виде крестиков.

На втором этапе строится непосредственно граф переходов. Для удобства перехода от размеченной граф-схемы алгоритма к графу переходов управляющего автомата вводится понятие пути от отметки ап к отметке а5 (от начального состояния к конечному):

(1) аn Х(ап, as) Y (am, as) as,.

где X (an, as) — конъюнкция всех логических условий Xk(k= 1, 2, 3,…), соответствующих условным вершинам на этом пути, причем Хк берут в прямой форме, если из данной вершины путь выходит по стрелке, отмеченной значением 1, и в инверсной форме, если путь выходит по стрелке, отмеченной значением 0;  - множество микроопераций, или микрокоманда, указанная в единственной операторной вершине, через которую проходит данный путь.

- множество микроопераций, или микрокоманда, указанная в единственной операторной вершине, через которую проходит данный путь.

Допустимы пути, содержащие несколько условных вершин или не содержащие ни одной, а также пути, не имеющие операторной вершины. Рассматриваются все пути, кроме тех, в которых некоторое условие  входит как в прямой, так и в инверсной форме. Множество путей (1) определяет множество переходов между состояниями

входит как в прямой, так и в инверсной форме. Множество путей (1) определяет множество переходов между состояниями  и

и  автомата. При построении графа переходов каждой отметке

автомата. При построении графа переходов каждой отметке  на граф-схеме алгоритма или состоянию

на граф-схеме алгоритма или состоянию  управляющего автомата ставят в соответствие вершину графа, а каждому пути (1) — дугу, направленную из вершины

управляющего автомата ставят в соответствие вершину графа, а каждому пути (1) — дугу, направленную из вершины  в вершину

в вершину  . Дуга отражает переход автомата из состояния

. Дуга отражает переход автомата из состояния  в состояние

в состояние  и помечается конъюнкцией

и помечается конъюнкцией  и выходными сигналами

и выходными сигналами  i. Если в рассматриваемом пути отсутствуют логические вершины, то полагают

i. Если в рассматриваемом пути отсутствуют логические вершины, то полагают  (т.е. осуществляется безусловный переход); если же отсутствует операторная вершина, то полагают

(т.е. осуществляется безусловный переход); если же отсутствует операторная вершина, то полагают  , где

, где  — пустой оператор, означающий сохранение состояния, так как не выполняется никакая микрооперация.

— пустой оператор, означающий сохранение состояния, так как не выполняется никакая микрооперация.

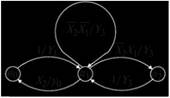

Построенный по изложенной методике граф переходов (рис. 5.7) определяет закон функционирования и структуру управляющего автомата.

Кодирование состояний управляющего автомата. Для фиксации состояний управляющего автомата будем использовать триггеры.

Рис. 5.6. Граф-схема алгоритма операции умножения двоичных чисел.

Рис. 5.7. Граф переходов.

Каждому состоянию управляющего автомата поставим в соответствие некоторую кодовую комбинацию, отображаемую состоянием 0-выходов триггеров. Число разрядов к кода, или триггеров, можно выбрать на основании соотношения  , где К — число состояний управляющего автомата. Для рассматриваемого случая К = 3, к = 2. Выбранные коды состояний управляющего автомата приведены в табл. 5.1.

, где К — число состояний управляющего автомата. Для рассматриваемого случая К = 3, к = 2. Выбранные коды состояний управляющего автомата приведены в табл. 5.1.

Таблица 5.1

Состояние | Код | ||

i. | ai | Q1 | Q0 |

a0 | |||

a1 | |||

a2 | |||

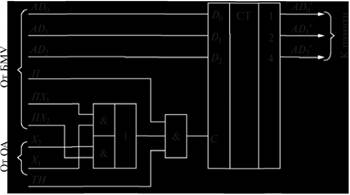

Структурная схема управляющего автомата представлена на рис. 5.8. Она содержит:

- • два RS-триггера

, образующих регистр хранения информации для фиксации текущего состояния управляющего автомата с помощью выходных сигналов

, образующих регистр хранения информации для фиксации текущего состояния управляющего автомата с помощью выходных сигналов  ;

; - • дешифратор, предназначенный для преобразования двухразрядного кода

в сигналы состояния

в сигналы состояния  ;

; - • комбинационную схему, которая вырабатывает управляющие сигналы

для операционного автомата и сигналы

для операционного автомата и сигналы  для триггеров по входным сигналам

для триггеров по входным сигналам

Дальнейшей задачей является построение комбинационной схемы. Составление таблицы функционирования комбинационной схемы. Задание работы управляющего автомата с помощью графа переходов обеспечивает наглядность. Однако при записи аналитических выражений для выходных сигналов управляющего автомата удобнее пользоваться таблицей функционирования (табл. 5.2). Каждая строка этой таблицы определяет один переход управляющего автомата.

В ней указываются исходное состояние  , его код

, его код  , состояние перехода

, состояние перехода  (конечное состояние) и его код

(конечное состояние) и его код  , входные сигналы X и выходные — Y и сигналы

, входные сигналы X и выходные — Y и сигналы  обеспечивающие изменение состояний триггеров. При составлении таблицы.

обеспечивающие изменение состояний триггеров. При составлении таблицы.

Рис. 5.8. Структурная схема управляющего автомата со схемной логикой.

функционирования используется граф переходов (рис. 5.7), а также сведения о кодировании состояний (табл. 5.1) и об изменении состояния триггеров (табл. 5.3, где Ф — любое значение сигнала: 0 или 1).

Таблица 5.2

№. п/п. | Начальное состояние ап и код ап. | Конечное состояние as и код as. | Логические условия X. | Микрокоманды Y. | Сигналы управления триггерами. S, R | ||||

|  |  |  |  |  | ||||

|  |  |  |  | |||||

|  |  |  |  | |||||

|  |  |  |  | |||||

|  |  |  |  | |||||

|  |  |  |  | |||||

Таблица 5.3

Вид перехода. | S. | R |

0 > 0. | Ф. | |

0 > 1. | ||

1 > 0. | ||

1 > 1. | Ф. |

В качестве примера покажем, как в табл. 5.2 заполняется графа «Сигналы управления триггерами 5, R» первой строки, которой соответствует переход из состояния  в

в  . Из таблицы видно, что младшие разряды

. Из таблицы видно, что младшие разряды  кодов

кодов  изменяются (0 > 1), старшие

изменяются (0 > 1), старшие  сохраняют свое значение (0 > 0). Так как триггер

сохраняют свое значение (0 > 0). Так как триггер  должен изменить состояние и имеет вид перехода 0 > 1, на его вход следует подать сигнал

должен изменить состояние и имеет вид перехода 0 > 1, на его вход следует подать сигнал  (табл. 5.3). Триггер

(табл. 5.3). Триггер  не изменяет состояния, поэтому на его входы сигналы не подаются. Следовательно, в графу «Сигналы управления триггерами S, R» первой строки заносится только

не изменяет состояния, поэтому на его входы сигналы не подаются. Следовательно, в графу «Сигналы управления триггерами S, R» первой строки заносится только

Запись логических выражений для комбинационной схемы. Для каждой строки табл. 5.2 запишем логическое выражение в следующей форме: в левой части выражения перечислим выходные величины Y, S, R (содержимое двух последних столбцов), в правой части — конъюнкцию  текущего (начального) состояния и условий перехода. В результате получим.

текущего (начального) состояния и условий перехода. В результате получим.

(2)

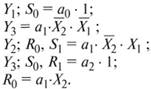

Пользуясь (2), составим логические выражения для каждой выходной величины комбинационной схемы. Для этого в левой части запишем непосредственно выходную величину, а в правой части — дизъюнкцию правых частей тех соотношений (2), в которые входит указанная выходная величина комбинационной схемы. Полученные таким образом логические выражения для комбинационной схемы имеют следующий вид:

(3)

Построение комбинационной схемы. Комбинационная схема строится по известным правилам с помощью выражений (3). Полная схема управляющего автомата со схемной логикой приведена на рис. 5.9. В комбинационную схему включен также дешифратор DC.

Рис. 5.9. Схема управляющего автомата со схемной логикой.

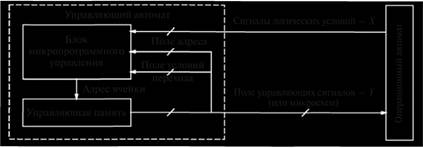

Управляющий автомат с программируемой логикой. Принцип построения управляющего автомата. В рассмотренном выше управляющем автомате со схемной логикой необходимая для работы операционного автомата последовательность управляющих сигналов формируется с помощью аппаратных средств. Рассмотрим другой принцип построения управляющего автомата, при котором генерирование управляющих сигналов задается микропрограммой, хранимой в ячейках управляющей памяти.

Совокупность управляющих сигналов  на каждом тактовом периоде образует микрокоманду. Последовательность микрокоманд, предназначенных для выполнения некоторой операции, называют микропрограммой. При этом выполнение операции сводится к последовательной выборке из управляющей памяти микрокоманд микропрограммы и выдаче с их помощью управляющих сигналов Y в операционный автомат. В управляющей памяти можно хранить много микропрограмм, предназначенных для выполнения различных операций. Выбор той или иной микропрограммы осуществляется с помощью команды, поступающей из оперативной памяти. Выбранная микропрограмма реализуется путем последовательного считывания микрокоманд микропрограммы из ячеек управляющей памяти. При таком принципе управления на каждом такте определяется адрес ячейки в управляющей памяти, откуда должна считываться следующая микрокоманда микропрограммы. Микрокоманда микропрограммы содержит ряд полей. Для каждого поля отведено определенное количество разрядов. Совокупность полей называют форматом микрокоманды. Как правило, в формате микрокоманды микропрограммы предусматриваются следующие элементы:

на каждом тактовом периоде образует микрокоманду. Последовательность микрокоманд, предназначенных для выполнения некоторой операции, называют микропрограммой. При этом выполнение операции сводится к последовательной выборке из управляющей памяти микрокоманд микропрограммы и выдаче с их помощью управляющих сигналов Y в операционный автомат. В управляющей памяти можно хранить много микропрограмм, предназначенных для выполнения различных операций. Выбор той или иной микропрограммы осуществляется с помощью команды, поступающей из оперативной памяти. Выбранная микропрограмма реализуется путем последовательного считывания микрокоманд микропрограммы из ячеек управляющей памяти. При таком принципе управления на каждом такте определяется адрес ячейки в управляющей памяти, откуда должна считываться следующая микрокоманда микропрограммы. Микрокоманда микропрограммы содержит ряд полей. Для каждого поля отведено определенное количество разрядов. Совокупность полей называют форматом микрокоманды. Как правило, в формате микрокоманды микропрограммы предусматриваются следующие элементы:

- • поле управляющих сигналов, представляющее собой микрокоманды У для управления операционным автоматом;

- • поле условий перехода, в котором указывается вид перехода: условный или безусловный. При условном переходе определяется логическое условие

, по которому осуществляется переход;

, по которому осуществляется переход; - • поле адреса, в котором указывается ориентировочный адрес следующей микрокоманды микропрограммы. В общем случае адрес зависит от логических условий. В зависимости от вида перехода и выполнения (невыполнения) логического условия указанный адрес сохраняется или модифицируется (изменяется).

Обобщенная структура управляющего автомата изображена на рис. 5.10 и включает в себя помимо управляющей памяти блок микропрограммного управления, основная функция которого состоит в формировании адреса следующей микрокоманды.

Рис. 5.10. Структура управляющего автомата с программируемой логикой.

По состоянию полей адреса и условий перехода текущей микрокоманды, а также по значению сигналов логических условий, выдаваемых операционным автоматом, в блоке микропрограммного управления формируется адрес ячейки памяти, в которой хранится следующая микрокоманда исполняемой микропрограммы. В следующем тактовом периоде микрокоманда считывается из управляющей памяти. Разряды поля управляющих сигналов поступают в операционный автомат, который выполняет данную микрокоманду Yk, а разряды поля адреса и поля условий перехода — в блок микропрограммного управления, который формирует адрес очередной микрокоманды. Процесс продолжается до тех пор, пока не будет выполнена вся микропрограмма. Поскольку структура управляющего автомата стандартна, основные усилия разработчика направлены на составление микропрограммы, которая записывается в ячейки постоянного запоминающего устройства.

Составим микропрограмму для выполнения операции умножения двоичных чисел по рассмотренному выше алгоритму, представленному на рис. 5.6.

Выбор формата и числа разрядов микрокоманды. Как отмечалось выше, в формате микрокоманды микропрограммы должно быть предусмотрено поле адреса, которое содержит код адреса следующей микрокоманды. Выберем число разрядов кода адреса, равное трем, что позволит хранить в управляющей памяти адреса до восьми микрокоманд.

Если выполнение микрокоманд не связано с логическими условиями, то адресный код А2А1А0 передается через блок микропрограммного управления в управляющую память без изменения. При наличии условного перехода адрес в блоке микропрограммного управления может быть изменен. По этой причине в формате команды предусмотрено поле условий переходов, содержащее три разряда П,  . Значение

. Значение  соответствует безусловному переходу. В этом случае разряды

соответствует безусловному переходу. В этом случае разряды  микрокоманды микропрограммы могут принимать любые значения (0 или 1). Значение

микрокоманды микропрограммы могут принимать любые значения (0 или 1). Значение  инициирует проверку логических условий

инициирует проверку логических условий  или

или  . При проверке логического условия

. При проверке логического условия  необходимо установить

необходимо установить  ; при проверке логического условия

; при проверке логического условия  . Следует отметить, что сигналы

. Следует отметить, что сигналы  логических условий формирует операционный автомат, а разряды

логических условий формирует операционный автомат, а разряды  проверки логических условий содержатся в микрокомандах микропрограммы, которая хранится в управляющей памяти (рис. 5.10).

проверки логических условий содержатся в микрокомандах микропрограммы, которая хранится в управляющей памяти (рис. 5.10).

В поле управляющих сигналов заносятся значения микрокоманд

или сигналов

или сигналов  активизирующих выполнение микроопераций. В табл. 5.4 приведен выбранный формат микрокоманды микропрограммы.

активизирующих выполнение микроопераций. В табл. 5.4 приведен выбранный формат микрокоманды микропрограммы.

Таблица 5.4

Формат микрокоманды микропрограммы. | ||||||||

Поле адреса. | Поле условий перехода. | Поле управляющих сигналов. | ||||||

|  |  |  |  |  |  |  |  |

|  |  | ||||||

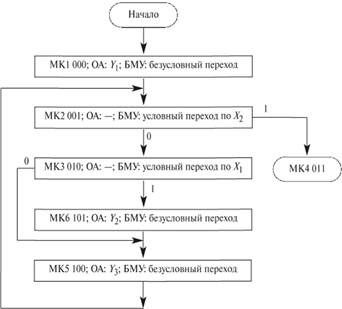

Разметка граф-схемы алгоритма. Каждой вершине граф-схемы алгоритма (рис. 5.6) операции умножения двоичных чисел, за исключением начальной, поставим в соответствие микрокоманду микропрограммы. Микрокоманды МК1, МК2, МКЗ… микропрограммы будем хранить в ячейках управляющей памяти с адресами 000, 001, 010… соответственно. Для обращения к ячейкам воспользуемся естественной адресацией, при которой различают микрокоманды двух типов: операционные и управляющие. Тип микрокоманды зависит от значения одноразрядного поля признака П: значению П= 0 соответствует операционная микрокоманда, значению  — управляющая микрокоманда. Операционная микрокоманда выполняется операционным автоматом под управлением сигналов

— управляющая микрокоманда. Операционная микрокоманда выполняется операционным автоматом под управлением сигналов  или микрокоманд

или микрокоманд  . Управляющая микрокоманда предназначена для реализации условных переходов в соответствии со значениями проверяемых условий

. Управляющая микрокоманда предназначена для реализации условных переходов в соответствии со значениями проверяемых условий  . При разметке граф-схемы алгоритма в каждую вершину вносится следующая информация:

. При разметке граф-схемы алгоритма в каждую вершину вносится следующая информация:

• записывается одна из микрокоманд микропрограммы и ее адресный код.

Номер микрокоманды и соответствующий ему адрес ячейки памяти проставляются согласно алгоритмической последовательности выполнения операции умножения. Если А — адрес текущей микрокоманды, то адрес следующей микрокоманды при безусловном переходе равен  , при условном переходе —

, при условном переходе —  ;

;

- • фиксируется состояние операционного автомата (ОА). В операторных вершинах проставляется операционная микрокоманда (

или

или  ), которую выполняет операционный автомат. В условных вершинах операционный автомат не выполняет микрокоманд, поэтому ставится прочерк «-» ;

), которую выполняет операционный автомат. В условных вершинах операционный автомат не выполняет микрокоманд, поэтому ставится прочерк «-» ; - • фиксируется состояние блока микропрограммного управления (БМУ). В операторной вершине выполняется безусловный переход, в условной вершине — условный переход. Поэтому делаются соответствующие записи и указывается, по какому условию (

или

или  ) выполняется управляющая команда.

) выполняется управляющая команда.

Размеченная по указанным правилам граф-схема алгоритма приведена на рис. 5.11. В операторную вершину с микрокомандой Y занесена первая микрокоманда МК1 и адрес ее ячейки памяти 000. В условной вершине  записана микрокоманда МК2 с адресом 001.

записана микрокоманда МК2 с адресом 001.

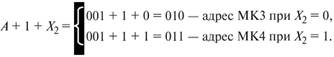

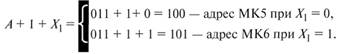

Адреса следующих двух микрокоманд определяются по приведенной выше формуле.

Следовательно, микрокоманда МК3 с адресом 010 заносится в вершину проверки логического условия  , а МК4 с адресом 011 — в вершину «Конец» (возможно, для выполнения другой микропрограммы).

, а МК4 с адресом 011 — в вершину «Конец» (возможно, для выполнения другой микропрограммы).

При вычислении адресов следующих двух микрокоманд необходимо иметь в виду, что последняя занятая ячейка памяти имеет адрес 011. Поэтому.

Следовательно, микрокоманда МК5 с адресом 100 заносится в вершину с микрокомандой  , а МК6 с адресом 101- в вершину с микрокомандой

, а МК6 с адресом 101- в вершину с микрокомандой

Составление микропрограммы. Микропрограмма составляется согласно размеченной граф-схеме алгоритма (рис. 5.11) и представляется в виде таблицы (табл. 5.5).

Рис. 5.11. Размеченная граф-схема алгоритма умножения двоичных чисел для составления микропрограммы.

В ячейку с адресом 000 помещаем МК1, которая в операционном автомате выполняет загрузку, предусмотренную управляющими сигналами  , а микрокоманда блока микропрограммного управления определяет безусловный переход (БП) к ячейке с адресом 001.

, а микрокоманда блока микропрограммного управления определяет безусловный переход (БП) к ячейке с адресом 001.

В ячейке 001 располагаем МК2, которая не предусматривает никаких действий в операционном автомате. Управляющая микрокоманда блока микропрограммного управления определяет условный переход по условию  : при

: при  происходит переход в следующую ячейку с адресом 010, при

происходит переход в следующую ячейку с адресом 010, при  — к ячейке 011, где хранится МК4 для продолжения программы после выполнения операции умножения.

— к ячейке 011, где хранится МК4 для продолжения программы после выполнения операции умножения.

Микрокоманда МКЗ в ячейке 010 также не предусматривает действий в операционном автомате и предназначена для осуществления перехода по условию  : при

: при  происходит переход к ячейке 100, при

происходит переход к ячейке 100, при  — к ячейке с адресом 101, где соответственно хранятся МК5 и МК6.

— к ячейке с адресом 101, где соответственно хранятся МК5 и МК6.

Микрокоманда МКЗ выполняет в операционном автомате действия, предусмотренные управляющими сигналами  , а в БМУ — безусловный переход к ячейке с адресом 001.

, а в БМУ — безусловный переход к ячейке с адресом 001.

Таблица 5.5

Адрес ячейки памяти. | Поле адреса. | Поле условий перехода. | Поле микрокоманд. | № МК. | ||||||

|  |  |  |  |  |  |  |  | ||

Ф. | Ф. | МК1. | ||||||||

МК2. | ||||||||||

МКЗ. | ||||||||||

МК4. | ||||||||||

Ф. | ф. | МК5. | ||||||||

Ф. | ф. | МК6. | ||||||||

Микрокоманда МК6 предусматривает в операционном автомате действия  , а в БМУ — безусловный переход к ячейке 100 (МК5). При отсутствии проверки логических условий

, а в БМУ — безусловный переход к ячейке 100 (МК5). При отсутствии проверки логических условий  значения

значения  и

и  могут быть любыми.

могут быть любыми.

Память для хранения микропрограммы. Как следует из табл. 5.5, для рассматриваемого операционного автомата в памяти должно храниться шесть микрокоманд. Помимо 3-разрядного адреса ( ) микрокоманда микропрограммы содержит 3-разрядное поле условий перехода (

) микрокоманда микропрограммы содержит 3-разрядное поле условий перехода ( ) и 3-разрядное поле микрокоманд

) и 3-разрядное поле микрокоманд  операционного автомата. Таким образом, необходимо хранить шесть 9-разрядных микрокоманд. В качестве памяти будем использовать комбинационную схему с 3 входами и 9 выходами, работа которой описывается таблицей истинности (см. табл. 5.6).

операционного автомата. Таким образом, необходимо хранить шесть 9-разрядных микрокоманд. В качестве памяти будем использовать комбинационную схему с 3 входами и 9 выходами, работа которой описывается таблицей истинности (см. табл. 5.6).

Таблица истинности составлена на основании микропрограммы, приведенной в табл. 5.5.

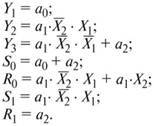

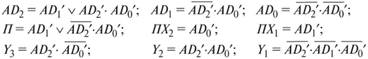

Используя карты Карно, можно получить следующие структурные формулы для комбинационной схемы [13]:

Построенная по структурным формулам комбинационная схема приведена на рис. 5.12. Схема имеет три адресных входа —

, на которые поступает модифицированный адрес из блока микропрограммного управления. С выхода комбинационной схемы снимается трехразрядный адрес (

, на которые поступает модифицированный адрес из блока микропрограммного управления. С выхода комбинационной схемы снимается трехразрядный адрес ( ), указанный в микропро;

), указанный в микропро;

Таблица 5.6

i | Входы. | Выходы. | ||||||||||

|  |  |  |  |  |  |  |  |  |  |  | |

Ф. | Ф. | |||||||||||

Ф. | Ф. | Ф. | Ф. | Ф. | Ф. | Ф. | Ф. | Ф. | ||||

Ф. | Ф. | |||||||||||

Ф. | Ф. | |||||||||||

Ф. | Ф. | Ф. | Ф. | Ф. | Ф. | Ф. | Ф. | Ф. | ||||

Ф. | Ф. | Ф. | Ф. | Ф. | Ф. | Ф. | Ф. | Ф. | ||||

Рис. 5.12. Комбинационная схема памяти.

грамме, сигн&чы проверки логических условий ( ) и микрокоманд (

) и микрокоманд ( ).

).

Блок микропрограммного управления (БМУ). Этот блок служит для модификации поступающего на его вход 3-разрядного адреса  . Логическая схема БМУ изображена на рис. 5.13. В нее входят:

. Логическая схема БМУ изображена на рис. 5.13. В нее входят:

• 3-разрядный счетчик СТ с тактовым входом С и тремя асинхронными входами  для загрузки 3-разрядного адреса

для загрузки 3-разрядного адреса  , поступающего из памяти;

, поступающего из памяти;

Рис. 5.13. Блок микропрограммного управления.

• логические элементы 2И-2И-ИЛИ и ЗИ. На их входы поступают логические условия  и сигналы

и сигналы  , инициирующие их проверку.

, инициирующие их проверку.

На каждом тактовом интервале адресный код  , считываемый из «ячейки» памяти (комбинационной схемы), поступает на входы БМУ и загружается в счетчик. Если в этой «ячейке» находится микрокоманда, связанная с проверкой логических условий (

, считываемый из «ячейки» памяти (комбинационной схемы), поступает на входы БМУ и загружается в счетчик. Если в этой «ячейке» находится микрокоманда, связанная с проверкой логических условий ( ,

,  ,

,  или

или  ), и значение проверяемого логического условия Х или равно 1, то адресный код на выходе БМУ увеличивается на 1:

), и значение проверяемого логического условия Х или равно 1, то адресный код на выходе БМУ увеличивается на 1:

Действительно, в этих случаях, как видно из схемы на рис. 5.13, логический элемент 3И открыт и тактовый импульс ТИ поступает на вход С счетчика, увеличивая его содержимое на единицу.

Во всех других случаях код сохраняется:  , так как логический элемент 3И закрыт и ТИ на вход Т счетчика не поступает.

, так как логический элемент 3И закрыт и ТИ на вход Т счетчика не поступает.

О расширении функциональных возможностей процессора. Рассмотренная структура в виде операционного и управляющего автоматов не только дает наглядное представление о принципах построения и функционирования процессора, выполняющего единственную операцию (команду, инструкцию) умножения двоичных чисел, но и указывает пути расширения его функциональных возможностей.

Для увеличения количества выполняемых операций необходимо прежде всего располагать операционным автоматом с более широкими функциональными возможностями. Таким операционным автоматом может служить арифметическо-логическое устройство (АЛУ), которое в большинстве случаев:

- • состоит из двоичного сумматора со схемами ускоренного переноса, регистров для временного хранения операндов и регистра-сдвигателя, комбинационных схем для выработки логических условий и работы с десятичной арифметикой;

- • выполняет операции арифметического сложения и вычитания, пересылки, логического И и ИЛИ, инверсии, сложения по модулю 2, сдвига и др.

Управляющий автомат можно строить на основе:

- • программируемой логики. В этом случае достаточно составить микропрограммы для требуемого набора операций (команд) и «зашить» их в постоянную память;

- • схемной логики для выполнения операций, которые требуют повышенного быстродействия.

Кроме того, необходимо дополнительно ввести:

- • внутреннюю память для хранения промежуточных результатов обработки;

- • средства коммуникации для пересылки данных между операционным автоматом и внутренней памятью.

Такой структурный состав имели первые поколения микропроцессоров.