Адресация к ячейкам памяти

При сигнале запись/считывание W#/R = 0 реализуется режим записи, так как активными являются усилители записи, на управляющие входы которых подается единичный сигнал. Снимаемые с прямых и инверсных выходов усилителей разряды входного слова DI поступают на элементы памяти ячейки ЯП2 и изменяют ее состояние в соответствии с поступившими данными. Рис. 9.6. Структура ОЗУ с двухкоординатной адресацией… Читать ещё >

Адресация к ячейкам памяти (реферат, курсовая, диплом, контрольная)

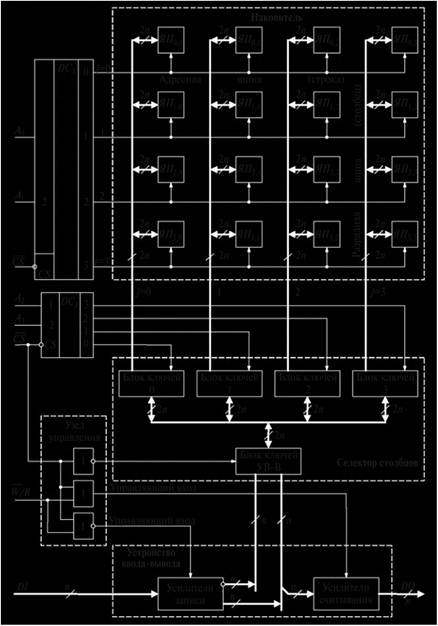

На рис. 9.6 приведена структура ОЗУ, иллюстрирующая принцип двухкоординатной адресации к ячейкам памяти.

Состав ОЗУ. Запоминающее устройство содержит:

- • накопитель, составленный из 16 ячеек памяти в виде матрицы 4×4. Каждая ячейка памяти предназначена для хранения n-разрядного слова. Предполагается, что элементы памяти выполнены на МОПтранзисторах по схеме, изображенной на рис. 92,а. Управляющие выходы элементов памяти (затворы МОП-транзисторов) соединены с адресной строкой, а два информационных выхода подключены к разрядным линиям, образующим 2n-разрядную шину для каждой ячейки. На рис. 9.6 шины выделены полужирной чертой с указанием числа линий в шине;

- • дешифраторы 2×4 строк DCX и столбцов DC у,

- • устройство ввода-вывода, состоящее из усилителей записи и считывания. Активному состоянию усилителей соответствует единичный сигнал на управляющем входе. Предполагается, что при подаче нулевого сигнала на управляющий вход усилители переводятся

Рис. 9.6. Структура ОЗУ с двухкоординатной адресацией к ячейкам памяти в высокоомное Z-состояние. Каждый усилитель записи имеет прямой и инверсный выходы. Входы усилителей считывания подключены к //-разрядной шине, по которой передается хранимое слово в прямом коде;

- • селектор столбцов, состоящий из 5 идентичных блоков ключей на МОП-транзисторах. Общее число ключей в блоке равно 2n, т. е. числу подводимых к блоку линий. Блоки ключей 0, 1, 2, 3 управляются выходными сигналами дешифратора столбцов DC у, позволяющими подключить одну из 4 ячеек памяти у-го столбца к устройству ввода-вывода (УВ-В). Подключение осуществляется через блок ключей У В-В, управляемый сигналом выбора микросхемы CS#;

- • узел управления, предназначенный для управления вводом-выводом информации (режимами работы ОЗУ).

Принцип работы ЗУ. Рассмотрим работу ЗУ в режимах записи, чтения и хранения. В режимах записи и чтения на входы ЗУ выставляется адресный код и сигнал выбора микросхемы CS# = 0. При этом с помощью дешифраторов DCX, DCy&kxw визируется одна из адресных строк и блок ключей, обслуживающий один из столбцов. В дальнейшем будем полагать, что активными являются строка / = 2 и столбец j = I. При выбранных условиях к устройству ввода-вывода подключается ячейка памяти, расположенная на пересечении 2-й строки и 1-го столбца, т. е. ЯП2.

При сигнале запись/считывание W#/R = 0 реализуется режим записи, так как активными являются усилители записи, на управляющие входы которых подается единичный сигнал. Снимаемые с прямых и инверсных выходов усилителей разряды входного слова DI поступают на элементы памяти ячейки ЯП2 и изменяют ее состояние в соответствии с поступившими данными.

При сигнале запись/считывание W#/R = 1 реализуется режим чтения, так как активными являются усилители считывания, на управляющие входы которых подается единичный сигнал. Усилители записи переводятся в высокоомное состояние и не влияют на протекающие процессы.

Таким образом, запись и считывание n-разрядных слов в ОЗУ отличается от рассмотренных выше операций записи и считывания отдельных бит (рис. 9.3) только тем, что используется п каналов вместо одного.