Адресация в микропроцессорах INTEL

Сегментная структура памяти обеспечивает возможность создания позиционно — независимых или динамически перемещаемых программ, что необходимо в мульти программной среде. Для этого все смещения в программе должны задаваться относительно фиксированных значений, находящихся в сегментных регистрах. Это позволяет произвольно перемещать программу в адресном пространстве памяти, изменяя только содержимое… Читать ещё >

Адресация в микропроцессорах INTEL (реферат, курсовая, диплом, контрольная)

Размещение байт и слов в памяти.

Память логически организована как одномерный массив байт, каждый из которых имеет 20-тибитовый физический адрес в диапазоне от 0 до FFFFF. Любые два смежных байта в памяти могут рассматриваться как одно 16-тиразрядное слово. Младший байт слова всегда имеет меньший адрес, а старший — больший адрес. Адресом слова считается адрес его младшего байта.

Сегментация памяти и вычисление адресов.

Пространство памяти емкостью в 1 Мб представлен как набор сегментов, определяемых программным путем.

Сегмент состоит из смежных ячеек памяти и является независимой и отдельно адресуемой единицей памяти объемом 64кб. Каждому сегменту программой назначается начальный (базовый) адрес — адрес 1-го байта сегмента. Начальные адреса 4-х сегментов, выбранных в качестве текущих записываются в сегментные регистры CS, DS, SS, ES.

ES. | ||

CS. | ||

SS. | ||

DS. | ||

В регистрах находятся базовые адреса для обращения к командам программы (CS), к данным (DS), стеку (SS), дополнительным данным (ES). Для обращения к командам и данным, находящимся в других сегментах, необходимо изменить содержимое сегментных регистров. Сегментные регистры инициализируются в начале программы засылкой в них соответствующих базовых адресов. В каждом сегментном регистре — 16 старших бит 20-разрядного начального адреса сегмента. 4 младших разряда адреса считаются =0 и автоматически приписываются справа к содержимому сегментного регистра при вычислении физических адресов.

Физический адрес ячейки памяти — это 20 — битовое число в диапазоне от 0 до FFFFF, которое однозначно определяет положение каждого байта в пространстве памяти емкостью до 1 Мб.

Логический адрес ячейки состоит из двух 16-битовых беззнаковых значений:

начального адреса сегмента (база) внутрисегментного смещения, которое определяет расстояние от начала сегмента до адресуемой ячейки.

Для вычисления физического адреса база сегмента сдвигается влево на 4 разряда и суммируется со смещением EA (это эффективный адрес, вычисляемый в соответствии с заданным способом адресации). Перенос из старшего бита при сложении игнорируется, что приводит к циклической организации памяти, когда за ячейкой с максимальным адресом следует ячейка с 0 адресом. Аналогичную кольцевую организацию имеет и каждый сегмент.

Пример вычисления физического адреса:

Смещение ЕА — эффективный адрес, вычисляемый в соответствии с заданным способом адресации.

Сегментная структура памяти обеспечивает возможность создания позиционно — независимых или динамически перемещаемых программ, что необходимо в мульти программной среде. Для этого все смещения в программе должны задаваться относительно фиксированных значений, находящихся в сегментных регистрах. Это позволяет произвольно перемещать программу в адресном пространстве памяти, изменяя только содержимое сегментных регистров. Стек организуется в ОЗУ по принципу скользящей вершины и его положение в ОЗУ определяется содержанием регистров SS (база) и SP (смещение). При этом SS регистр хранит базовый адрес текущего сегмента стека, а регистр SP указывает на вершину стека. При каждом обращении к стеку пересылается 1 слово, причем содержимое SP изменяется автоматически: при записи в стек слова содержимое SP уменьшается на два, а при чтении из стека — увеличивается на два.

Форматы команд микропроцессора INTEL.

Регистры общего назначения (РОНы) разбиты на две группы:

- 1. группа HL, состоящая из регистров AX, BX, CX, DX, которые предназначены для хранения данных и допускают раздельную адресацию их старших Н и младших L половин.

- 2. группа PI, содержащая указательные регистры BP, SP и индексные регистры SI, DI, в которых обычно храниться адресная информация.

15 8 7 0. | ||||

AH. | AL. | АХ — аккумулятор | ||

CH. | CL. | СХ. | ||

DH. | DL. | DX. | ||

DH. | BL. | ВХ. | ||

SP. | Адресный регистр | |||

BP. | Адресный регистр | |||

SI. | Адресный регистр | |||

DI. | Адресный регистр | |||

Команды могут адресовать один или два операнда. В двухоперандных командах один из операндов должен обязательно располагаться в регистре, поскольку имеются команды типа регистр-регистр, регистр-память, память регистр, но команда типа память-память отсутствует, за исключением команд пересылки цепочки байт ил слов.

Формат двухоперандной (двуядерной) команды имеет следующий вид:

Cop dw. | md reg r/m. | Disp L. | Disp H. | |

Первый байт команды содержит Cop — код операции и два однобитовых поля: dбит направления передачи и wдлина операнда.

При d=1, то осуществляется передача операнда или результата операции в регистр, номер которого задается полем reg второго байта команды.

При d=0, то осуществляется передача операнда или результата из адресуемого полем reg регистра.

Поле W идентифицирует тип (разрядность) операндов:

Если w=1, то команда оперирует с 2-хбайтным словом.

w=0, команда оперирует с 1 байтом.

2-ой байт — постбайт, определяет участвующие в операции регистры или регистр и ячейку памяти. постбайт состоит из 3-х полей:

md — режим, показывающий как интерпретируется поле r/m для нахождения первого операнда.

Reg — регистр, используется в 2 -х операндных командах.

R/m — регистр/память Поле reg определяет операнд, который обязательно находится в регистре микропроцессора и считается вторым операндом. Поле r/m определяет операнд, который может находится в регистре или памяти и условно считается первым. Поле reg используется только для указания регистра в двухоперандных командах. Если в команде один операнд, то он идентифицируется полем R/m, а поле reg отсутствует. Вместо поля reg в этом случае используется расширение кода операции.

Поле md (модальность) показывает, как интерпретируется поле R/m для нахождения первого операнда:

Если md=11, то операнд находится в регистре, номер которого задан полем R/m. При других значениях md операнд находится в памяти.

Когда адресуется память, то поле md определяет вариант использования смещения disp, находящегося в 3 и 4 байте.

Disp — смещение в команде, интерпретируемое как целое число со знаком.

md=00 смещение disp отсутствует.

md=01 disp =disp L, команда содержит 8 бит, смещение D8.

md=10 disp= dispH dispL, команда содержит 16 бит, смещение D16.

Режимы адресации (вычисление эффективного адреса ЕА)

Поле md. | ||||||

R/m. | md=00. disp=0. | md=01. dispH=dispL=D8. | md=10. disp=dispH dispL. | |||

W=1. | W=0. | |||||

BX+SI. | BX+SI+D8. | BX+SI+D16. | AX. | AL. | ||

BX+DI. | BX+DI+D8. | BX+DI+D16. | CX. | CL. | ||

BP+SI. | BP+SI+D8. | BP+SI+D16. | DX. | DL. | ||

BP+DI. | BP+DI+D8. | BP+DI+D16. | BX. | BL. | ||

SI. | SI+D8. | SI+D16. | SP. | AH. | ||

DI. | DI+D8. | DI+D16. | BP. | CH. | ||

DI6. | BP+D8. | BP+D16. | SI. | DH. | ||

BX. | BX+D8. | BX+D16. | DI. | BH. | ||

Приведенные в таблице правила имеют одно исключение, позволяющее реализовать прямую (абсолютную) адресацию: если md=D16=dispH dispL.

Таким образом, имеется три варианта интерпретации поля md и восемь вариантов интерпретации поля r/m, что дает 24 варианта вычисления эффективного адреса ЕА.

Команды микропроцессора реализуют разные способы адресации, что упрощает организацию и использование сложных структур данных и расширяет возможности отдельных команд, и повышает гибкость их применения.

регистровая адресация. Операнд находится в одном из РОНов или сегментном регистре. Регистр может быть определен в байте кода операции или постбайте (3-битными полями) reg и r/m при условии md=11. Команды, оперирующие содержимым регистров, короткие и быстрые, так как не требуют вычисления эффективного адреса ЕА, и обращения к памяти.

Непосредственная адресация. Непосредственные операнды — это const длиной 8 или 16 бит, которые размещаются в последних байтах команды.

Cop sw. | md cop r/m. | Disp L. | Disp H. | Data L. | Data H. | |

Так как 2-ой операнд размещается в команде, то поле reg отсутствует, но вместо него используется расширение кода операции cop. Отсутствует бит направления d, так как результат операции можно поместить только на место первого операнда. Место этого бита d занимает бит S, который является признаком использования одного байта для задания непосредственного операнда при работе со словами.

Поля S и W интерпретируются следующим образом:

SW=Х0, один байт данных Data L.

SW=01, один байт данных Data H Data L.

SW=11, один байт данных, который автоматически расширяется со знаком до 16 бит.

прямая адресация. Эффективным адресом ЕА является содержание байта в смещении disp команды. Реализуется при использовании постбайта с полями md=00 и r/m=10.

Косвенно-регистровая адресация. Эффективный адрес ЕА равен содержимому одного из регистров SI, DI, BX при md=00 и r/m=100, 101, 111.

Базовая адресация ЕА вычисляется суммированием содержимого регистров BX и BP со смещением disp при md=01 и 10, r/m=100 и 111.

Индексная адресация ЕА вычисляется суммированием индексных регистров SI и DI и смещения disp при md=01 и 10 при r/m=100, 101.

Базовая индексная адресация. ЕА равно сумме содержимого базовых регистров BX или BP, индексного регистра SI или DI и смещения disp. Реализуется при md не равного 11 и r/m=000, 001, 010, 011.

Сегментная организация памяти.

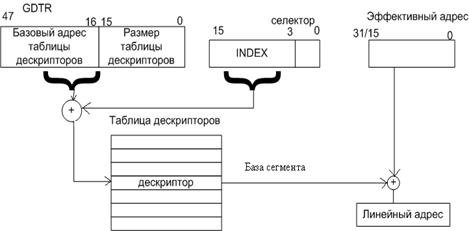

В защищенном режиме для формирования линейного адреса используется две компоненты:

- 1)16-тиразрядный селектор для определения базового адреса сегмента, который содержится в дескрипторе.

- 2)16 или 32-хразрядный эффективный адрес, который зависит от режима работы и способа адресации.

Проиллюстрируем процесс вычисления линейного адреса с помощью следующей схемы:

Для получения линейного адреса базовый адрес сегмента, содержащийся в дескрипторе, суммируется с эффективным адресом.

При отсутствии страничной организации памяти линейный адрес является физическим адресом для обращения к элементу памяти.

Страничная организация памяти.

Страничный диспетчер памяти, имеющийся в микропроцессоре, обеспечивает следующую возможность:1)представляет пользователю возможность работать с большим адресным пространством;

- 2)обеспечивает защиту ОС и программное обеспечение пользователя;

- 3)реализует быструю трансляцию адресов.

Линейное адресное пространство памяти объемом 4 Гб при страничной организации разбито на 220 страниц объемом по 4 кб каждая страница. Фиксированный размер всех страниц позволяет загружать любую требуемую виртуальную страницу в нужную физическую страницу.

Страничная трансляция включается в защищенный режим установкой в единицу 31-го разряда нулевого регистра управления CRQ и выключается сбросом этого разряда в ноль.

При страничной организации сегмент разбивается на отдельные разделы, число которых может достигнуть до 210.

В свою очередь каждый раздел может содержать до 210 страниц объемом по 4 кб каждая. Начальные (базовые) адреса страниц каждого раздела хранятся в соответствующей таблице страниц, содержащейся в памяти. Обращение к этой таблице производится с помощью каталога, в котором содержатся начальные адреса таблиц страниц для всех разделов. Таким образом, страницы могут быть рассеяны по разным частям памяти, а их размещение в памяти определяется содержимым каталогов разделов и таблиц страниц.

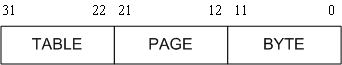

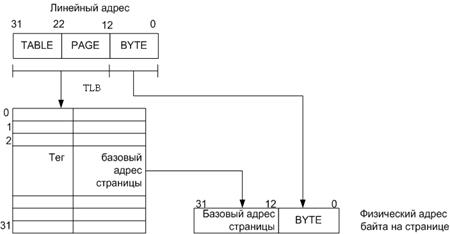

Линейный 32-ый адрес при страничной организации памяти является исходной информацией для формирования физического адреса с помощью каталога разделов и таблиц страниц. При этом линейный адрес рассматривается как совокупность трех полей.

TABLE — указывает относительный адрес таблицы страниц выбираемого раздела в каталоге.

PAGE — задает относительный адрес требуемой страницы данного раздела.

BYTE — содержит относительный адрес выбираемого на странице байта.

Каталог занимает одну страницу памяти, где для каждого раздела содержатся 32-разрядные указатели входа в таблицу страниц этого раздела. Каждая из таблиц страниц также занимает одну страницу памяти, где для каждой страницы дается 32-хразрядный указатель входа в эту страницу.

Указатели входа в раздел и в страницу имеют одинаковый формат.

Каждый указатель содержит информацию, определяющую порядок использования страниц. Старшие 20 разрядов занимает базовый адрес. Остальные разряды имеют следующий смысл.

Р — бит присутствия. Если Р=1, то разрешается использование таблицы страниц, если Р=0, то такое использование запрещается. При Р=0 попытка обращения к соответствующему разделу или странице вызывает прерывание из-за отсутствия нужной страницы в оперативной памяти. После загрузки нужной страницы в память, бит Р устанавливается в «1» и в этом случае обращение к данной странице становится возможной. Это нужно для того, чтобы ОС знала, где находится страница.

R/W — бит чтения/записи.

U/S — бит пользователь/супервизор.

Эти два бита определяют право доступа к соответствующей странице или разделу для программ пользователя. Программа пользователя обычно имеет самый низкий уровень привилегий равный 3. Если осуществляется запрос с уровнем привилегий равным 3, то при значении U/S = 0 программе пользователя запрещается доступ к разделу или странице.

При U/S = 1 обращение разрешается, но при этом учитывается значение бита R/W.

Если R/W = 0, то программе пользователя разрешается только чтение раздела или страницы.

Если R/W = 1, то разрешается как чтение, так и запись. Если осуществляются запросы с большим уровнем привилегий (0, 1 и 2), то допускается запись и чтение разделов и страниц при любых значениях `1' и `2' разрядов.

Такие уровни привилегий имеет ОС.

А — бит доступа. Этот бит автоматически устанавливается в «1» микропроцессором при обращении к данному разделу или странице для записи или чтения.

D — бит «мусора». В указателе кадра страницы этот бит устанавливают в «1» при записи на данную страницу. Для указателей таблиц страниц значение бита D является неопределенной.

Биты D и A используются ОС, поддерживающей виртуальную память, для определения в ОЗУ тех разделов и страниц, которые подлежат удалению из ОЗУ, поскольку к ним долгое время не было обращения. Проверку и сброс этих разрядов выполняет ОС. Проиллюстрируем процесс вычисления физического адреса с помощью следующей схемы:

Содержимое CR3 (регистр управления) задает старшие 20 разрядов базового адреса для входа в каталог раздела. Для получения физического адреса строки каталога разделов к этим 20 разрядам добавляется 10-тиразрядное поле TABLE линейного адреса и 2 нулевых младших разрядов. По полученному таким образом адресу обращаются к каталогу разделов, откуда выбирают указатели входа в таблицу страниц. Этот указатель содержит 20-разрядный базовый адрес таблицы страниц. К этим 20 разрядам добавляется поле PAGE и 2 нулевых младших разряда. В результате получается адрес строки таблицы страниц. В этой строке находится указатель входа в страницу, содержащий 20-разрядный базовый адрес страницы. Добавление к этому базовому адресу 12-тиразрядного поля BYTE дает физический адрес байта.

Существенное сокращение времени преобразования адресов в микропроцессоре достигается путем внутренней ассоциативной памяти, которая называется «буфером ассоциативной трансляции» и обозначается TLB.

TLB представляет собой память с ассоциативной выборкой, которая содержит 20-тиразрядные базовые адреса 32-х страниц, то есть, старшие 20 разрядов физического адреса страницы. Каждый из базовых адресов имеет свой признак (тег). В качестве тега используются старшие 20 разрядов линейного адреса, то есть поля TABLE и PAGE. Формирование физического адреса с использованием TLB производится следующим образом:

При поступлении в блок управления страницами линейного адреса его старшие 20 разрядов сравниваются с тегами физических адресов, хранящихся в TLB. Если обнаруживается совпадение этих разрядов с каким-либо из тегов, то из TLB выбирается соответствующий этому тегу базовый адрес. Страничный диспетчер формирует 32-хразрядный физический адрес, в котором выбранный из TLB базовый адрес задает 20 старших разрядов, а поле BYTE линейного адреса — 12 младших разрядов.

Случай, когда базовый адрес страницы находится в TLB, называется КЭШ-попаданием. При этом не требуется обращаться к ОЗУ для выборки указателя входа в таблицу страниц и в саму страницу.

Если базовый адрес нужной страницы отсутствует в TLB, то такое обращение называется КЭШ-промахом. При этом микропроцессор выполняет описанную выше процедуру формирования физического адреса с помощью каталога разделов и таблиц страниц. Полученный при этом из таблицы страниц 20 — разрядный базовый адрес вместе с соответствующими 20 разрядами старшей части адреса (тегом) записывается в свободную или дольше других занимаемую ячейку TLB. Таким образом, обеспечивается непрерывное обновление содержимого TLB.

Помимо тега для каждого базового адреса страницы в TLB хранится дополнительная информация, позволяющая определить, какую страницу можно заменить на вновь вводимую. Поскольку TLB хранит адреса только 32 страниц объема 4 кб каждая, то микропроцессор может непосредственно формировать физические адреса для 128 кб памяти (4×32). При этом по статистике вероятность КЭШ попадания равна 0,98 и, следовательно, только 2% обращений вызывают КЭШ промах и требуют двухступенчатого преобразования адресов.