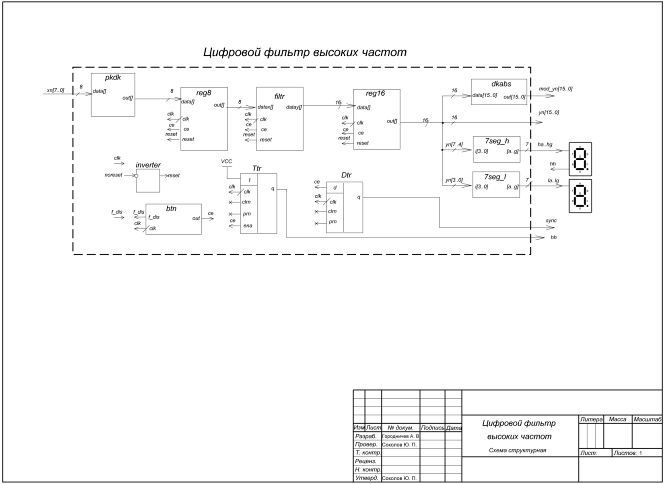

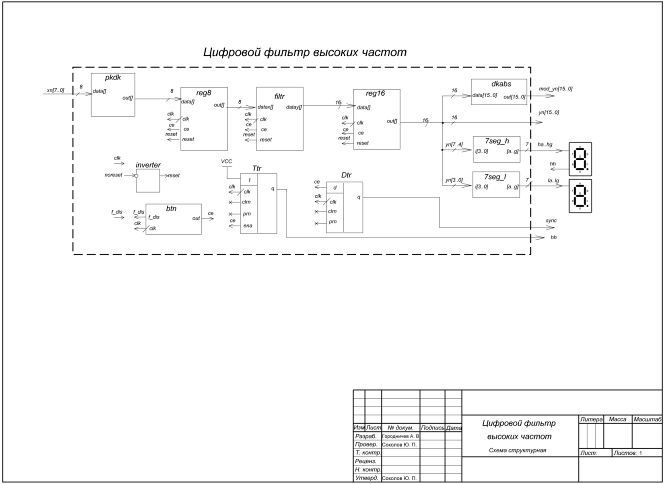

filtr.

Обработку входящих данных будет осуществлять блок filtr, являющий непосредственно фильтром высоких частот, преобразующим 8-разрядные данные в 16-разрядные.

xn, yn — последовательности 8-разрядных входных и 16-разрядных выходных данных.

pkdk.

Поскольку MaxII plus работает с числами в дополнительном коде, а входные данные требуется подавать в прямом коде, то необходим преобразователь чисел из прямого кода в дополнительный.

dkabs.

Он необходим для того, чтобы отрицательные значения корректно отображались, например, вместо числа -322 = 1111 1110 1011 1110 = мы получим 33 090. Поэтому добавим блок dkabs, который будет являться модулем выходных значений.

reg8, reg16.

Входная последовательность подается на фильтр асинхронно, с различными задержками, а сам фильтр является синхронным устройством, поэтому для синхронизации входных и выходных данных требуются регистры, с разрядностью 8 и 16 соответственно.

btn.

После нажатия кнопки происходит ряд ложных отскоков, следовательно требуется установить антидребезговое устройство для формирования из асинхронного сигнала f_dis синхронный се.

Dtr.

Для задержки сигнала на выходе на 1 такт требуется 1 D-триггер.

7seg_h, 7seg_l.

Контроль выходных данных осуществляется на семисегментных индикаторах, 7seg_h — отображает старший (high) разряд, 7seg_l — отображает младший разряд (low).

Ttr.

Т-триггер используется для проверки выработки ce. Выход триггера подключается к разъему hh одного из семисегментных индикаторов. Получается, что при каждом новом такте ce потенциал на разъеме будет менять своё состояние. Сигнал се разрешает прием входных данных. Контроль каждого сигнала позволяет судить о том, что мы считываем именно реальные данные, а не ложные, например, результаты переработки.

noreset.

Для управления триггерами требуются внешние установочные сигналы [3]. При назначении 0 сигналу noreset, триггеры устанавливаются в начальное состояние (0, 0 — на входах R и S соответственно).

tr[]. (clk, clrn, ena) = (clk, noreset, ce).

Структурная схема устройства изображена на рисунке 9.

Рисунок 9. Структурная схема фильтра.