Методы записи в КЭШ память

При обращении селектора к таблице GDT сдвинутый на 3 разряда влево (умноженный на 8) селектор служит в качестве смещения для формирования адреса дескриптора. Это смещение сравнивается с границей (с размером) таблицы дескрипторов, находящейся в разрядах с 0 по 15 регистра GDTR. Если смещение превышает границу, то вырабатывается соответствующее прерывание. Если нарушения границы нет, то смещения… Читать ещё >

Методы записи в КЭШ память (реферат, курсовая, диплом, контрольная)

При работе с КЭШ памятью преобладают операции чтения, а операции записи составляют меньше 10% трафика памяти. Операция чтения происходит за меньшее время, чем операция записи, поскольку строка из КЭШ памяти может быть прочитана в то же самое время, когда читаются и сравниваются теги строки и адреса. При КЭШ попадании прочитанная строка или ее часть немедленно передаются процессору. При КЭШ промахе от заранее прочитанной строки нет никакой пользы.

При записи новой информации в КЭШ операция сравнения тегов должна предшествовать всем остальным действиям, поскольку проверка тегов не может выполняться параллельно с другой работой, то операция записи занимает больше времени, чем операция чтения.

Возможны два способа записи в КЭШ память:

- 1)метод сквозной записи;

- 2)метод обратной записи.

Первый метод предполагает наличие двух копий данных: одной в КЭШ памяти, а другой в ОЗУ. Запись выполняется одновременно и в КЭШ и в ОЗУ. В результате системная шина и процессор работают с большой нагрузкой, поскольку на каждую операцию изменения данных приходится две операции записи. Метод сквозной записи имеет преимущество в том, что ОЗУ всегда имеет свежую копию данных, что важно в мультипроцессорных системах и при организации ввода-вывода данных. Кроме того сквозная запись имеет простую схемную реализацию. Такой метод записи использовался в 80 486 микропроцессоре фирмы Intel.

При использовании метода обратной записи цикл записи происходит только в КЭШ памяти, если в КЭШе находится строка, к которой идет обращение (КЭШ попадание). Если адресуемой строки в КЭШ нет, то информация записывается сразу в ОЗУ. При КЭШ попадании запись в ОЗУ происходит только при замещении строки КЭШа. Для сокращения частоты копирования строк запись в ОЗУ происходит только в том случае, если замещаемая строка КЭШа была модифицирована, то есть изменена. Для определения факта изменения строки с каждой строкой КЭШа связывают так называемый «бит модификации». Этот бит показывает, была ли изменена строка в КЭШ памяти или нет. Если строка в КЭШ не модифицирована, то обратное копирование отменяется, поскольку ОЗУ содержит туже самую информацию, что и КЭШ память.

Преимущество данного метода заключается в том, что запись выполняется со скоростью КЭШ памяти. А несколько записей на одну и туже строку КЭШа требует только одной записи — в ОЗУ, что снижает загрузку системной шины. Запись с обратным копированием используется в Pentium.

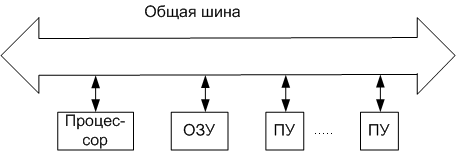

Архитектура миниЭВМ с общей шиной.

Интерфейс общая шина обеспечивает связь между процессором, ОЗУ и ПУ. Для всех передач информации между данными устройствами используются одни и те же линии, процедуры, команды и управляющие силы. При этом в данный момент времени передача информации возможна только между двумя устройствами через общий интерфейс, причем одно из этих устройств является задатчиком (ведущим), а другое — исполнителем (ведомым). Исполнителем может быть любое устройство, подсоединенное к интерфейсу, а задатчиком любое устройство, кроме ОЗУ.

Роль устройств в процессе передачи данных постоянно меняется. Например, при чтении информации из ОЗУ процессор является задатчиком, а ОЗУ — исполнителем. При получении сигнала прерывания от ПУ процессор становится исполнителем, а ПУ — задатчиком.

В процессоре имеется восемь 16-тиразрядных универсальных РОНов, которые нумеруются, как R0, R1…, R7. Эти регистры могут быть использованы как аккумуляторы, индексные регистры, указатели адресов, таблиц, списков, стеков и так далее. Конкретные использования регистров зависит от выбранного режима адресации. Особые функции имеет регистр R7, который используется в качестве счетчика команд, то есть содержит адрес следующей исполняемой команды.

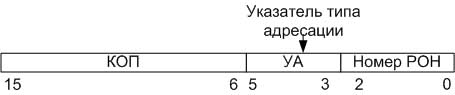

В процессоре используется 16-тиразрядный формат команд, и принята адресация через один из РОНов. Номер этого регистра указывается в формате команды. В качестве примера приведем формат одноадресной команды.

КОП — код операции.

Указатель типа адресации (УА) занимает три разряда, что позволяет задать восемь режимов адресации.

Режим адресации определяет способ интерпретации содержимого выбранного РОНа.

Особенности адресации миниЭВМ PDP-11.

Кроме одноадресных команд в PDP-11 используются также и двухадресные команды. Приведем формат двухразрядной команды.

В двухразрядных командах режимы адресации могут быть разными.

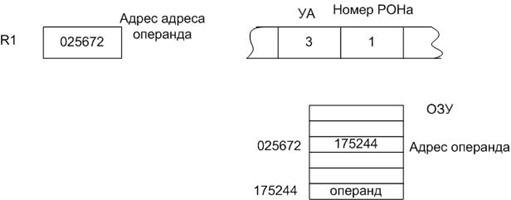

В командах широко используется косвенная адресация, то есть, когда в адресуемом РОНе находится не операнд, и даже не адрес операнда, а адрес адреса операнда. Формально, когда в РОНе находится адрес операнда, такая адресация уже является косвенной. Однако, поскольку РОНы находятся внутри процессора на обращение к ним затрачивается минимум времени, то РОНы могут рассматривать как продолжение самих команд.

Рассмотрим различные варианты адресации.

1. «Регистровая прямая».

В этом случае в адресуемом РОНе находится операнд.

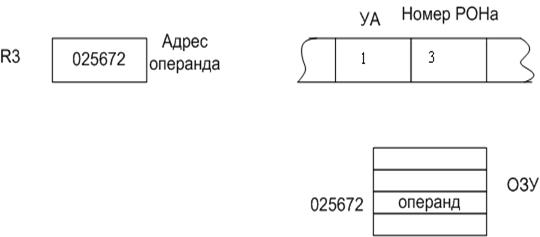

2. «Регистровая косвенная».

Операнд находится в памяти по адресу, содержащемуся в адресуемом РОНе.

3. «Автоинкрементная косвенная».

Операнд находится в памяти по адресу, который находится в другой ячейке памяти, на которую указывает содержимое выбранного РОНа.

Приведем таблицу, в которую сведены все восемь основных типов адресации.

Прямые режимы. | Косвенные режимы. | |||||||

УА. | Мнемоника. | Тип адресации. | Описание типа адресации. | УА. | Мнемоника. | Тип адресации. | Описание типа адресации. | |

Rn. | Регистровая прямая. | Содержимое РОНа Rn является операндом. | @Rn. | Регистровая косвенная. | Содержимое Rn является адресом операнда. | |||

(Rn)+. | Автоинкрементная прямая. | Содержимое Rn используется как адрес операнда, а затем увеличивается на единицу (при адресации байта) или на два (при адресации слова). | @(Rn)+. | Автоинкрементная косвенная. | Содержимое Rn используется как адрес адреса операнда, а затем увеличивается на два. | |||

— (Rn). | Автодекрементная прямая. | Содержимое Rn уменьшается на 1 или 2, а затем новое содержимое используется как адрес операнда. | @ - (Rn). | Автодекрементная косвенная. | Содержимое Rn уменьшается на 2, а затем новое содержимое используется как адрес адреса операнда. | |||

X (Rn). | Индексная прямая. | Содержимое Rn суммируется с содержимым ячейки ОЗУ Х, следующей непосредственно за первым или вторым словом команды. Получаемая сумма используется как адрес операнда. | @X (Rn). | Индексная косвенная. | Содержимое Rn (индекс) суммируется с содержимым ячейки ОЗУ Х (приращением), следующей непосредственно за первым или вторым словом команды. Получаемая сумма используется как адрес операнда. | |||

При использовании содержимого РОНа в качестве адреса или адреса адреса операнда необходимо предварительно занести этот адрес в выбранный РОН. Поскольку на это занесение требуется определенное дополнительное время, то указанный способ адресации применяется только при обработке массивов информации. Например, при обработке матриц или БД. В этом случае однажды установленный адрес в РОНе может многократно автоматически увеличиваться, адресуя различные операнды. При этом содержимое РОНа изменяется на 1-цу при адресации байт или на 2 при адресации слов.

Следует отметить, что при использовании косвенных режимов 3 и 5 увеличение содержимого РОНа всегда производится на 2, поскольку в этом случае РОН содержит адрес адреса, который является 16-ти разрядным.

При использовании индексной адресации команда как бы увеличивается до 2 или 3 слов, поскольку приращение Х можно рассматривать как продолжение команды. Если индексную адресацию имеет только один операнд, применяются двухсловные команды, в которых приращение Х помещается во второе слово. Если оба операнда имеют индексную адресацию, то используются трехсловные команды, причем для адресации источника используется второе, а для адресации приемника — третье слово команды.

) 1-ое слово команды. | Одна трехсловная команда, когда оба адреса имеют индексное приращение x1 и x2. | |

+2) Х1 — первое приращение. | ||

+4) Х2 — второе приращение. | ||

Рассмотрим некоторые примеры использования режимов адресации.

Одноадресные команды.

INC — к содержимому приемника прибавляется 1. (операнд, записанный по адресу приемника, увеличивается на 1).

1.1. Регистровая прямая (УА=0).

INC R3.

До операции (R3)=777, тогда после операции (R3)=1 000.

1.2. Автоинкрементная косвенная (УА=3).

INC @R3+.

До операции (R3)=1 000, тогда после операции (R3)=1 002.

Содержимое R3 является адресом адреса операнда.

(1 000)=2 000.

До операции (2 000)=2 002, после операции (2 000)=2 003.

Для работы с отдельными ячейками ОЗУ в качестве РОНа может использоваться и регистр R7 (счетчик команд). Этот счетчик всегда содержит адрес ячейки следующей за выполняемой командой. Счетчик можно использовать в любом из основных режимов адресации. Однако на практике целесообразно работа СК только в 4-х из этих режимов. Поэтому с точки зрения программиста возможны 4 дополнительных режима адресации через счетчик команд:

- 1)непосредственный;

- 2)абсолютный;

- 3)относительный;

- 4)косвенно-относительный.

Аппаратурно эти 4 режима ничем не отличаются от соответствующих режимов с использованием других регистров процессора.

Дополнительные типы адресации можно свести в таблицу.

УА. | Мнемоника. | Основной режим обработки. | Описание типа адресации. | Основной тип адресации. | |

#A. | Автоинкрементная прямая с R7. | Содержимое ячейки, следующей за 1-ым или 2-ым словом команды является операндом. | Непосредственная адресация б) первое слово команды б+2) операнд А1. б+4) операнд А2. | ||

@#A. | Автоинкрементная косвенная с R7. | Содержимое ячейки, следующей за 1-ым или 2-ым словом команды является адресом операнда. | Абсолютная адресация б) первое слово команды б+2) адрес операнда А1. б+4) адрес операнда А2. | ||

A. | Индексная прямая с R7. | Содержимое ячейки, следующей за 1-ым или 2-ым словом команды суммируется с содержимым R7 (СК) и полученная сумма используется как адрес операнда. | Относительная адресация б) первое слово команды б+2) ?А1=А1-(б+4). б+4) ?А2=А2-(б+6). | ||

@A. | Индексная косвенная с R7. | Содержимое ячейки, следующей за 1-ым или 2-ым словом команды суммируется с содержимым R7 и полученная сумма используется как адрес адреса операнда. | Косвенно-относительная адресация. ) 1-ое слово команды. +2) ?А1=А1-(+4). +4) ?А2=А2-(+6). | ||

При выполнении команд с непосредственной адресацией после выборки первого слова команды, содержимое СК автоматически увеличивается на 2. Содержимое СК интерпретируется как адрес операнда. То есть, операндом является второе слово команды. Таким образом, этот режим позволяет задавать операнды в программе путем запоминания операнда во втором слове команды с автоматическим увеличением СК еще на 2. Это увеличение на 2 необходимо, чтобы СК указывал на следующую команду, а не на второе слово текущей команды.

) 1-ое слово команды. | |

+2) — константа (операнд). | |

+4) — следующая команда. | |

В режиме абсолютной адресации операция выполняется аналогично предыдущему режиму. Однако, содержимое СК интерпретируется как адрес адреса операнда, то есть адресом является 2-ое или 3-е слово команды. В отличие от предыдущего режима во втором и третьем слове команды находятся адреса операндов:

) 1-ое слово команды. | ||

+2) А1. | А1 и А2 -это абсолютные адреса в трехсловной команде. | |

+4) А2. | ||

+6) — следующая команда. | ||

В режиме относительной адресации после выборки 1-ого слова команды и увеличения содержимого СК на 2, процессор вновь обращается в ОЗУ за индексным словом Х по адресу, содержащемуся в СК. СК получает приращение на 2. Процессор суммирует выбранное индексное слово Х (то есть, 2-ое слово команды А1) с содержимым СК. Полученная сумма является адресом операнда:

(СК) + ?А1=(+4)+А1-(+4)=А.

) 1-ое слово команды. | |

+2) ?А1=А1-(+4). | |

+4) ?А2=А2-(+6). | |

+6) ; | |

Если команда трехсловная, то описанная процедура проделывается и над 3-им словом команды и содержимым СК.

Косвенно-относительный режим адресации аналогичен предыдущему с той лишь разницей, что сумма индексного слова Х и содержимого СК интерпретируется как адрес адреса операнда.

Относительный режим адресации используется при написании позиционно-независимых программ, то есть, программ, место расположение которых не зависит от их нахождения в ОЗУ.

Некоторые команды.

мнемоника. | Код операции. | Название команды. | ||

1). | CLR. CLRB. |

| Очистка слова (2б) Очистка байта (1б). | |

2). | INC. INCB. |

| Увеличение слова на 1. Увеличение байта на 1. | |

3). | DEC. DECB. |

| Уменьшение слова на 1. Уменьшение байта на 1. | |

4). | MOV. MOVB. |

| Пересылка слова (А1) в (А2). Пересылка байта. | |

5). | ADD. | Сложение (А1) + (А2) в А2. | ||

6). | SUB. | Вычитание (А2) — (А1) в А2. | ||

Архитектура микропроцессора 80i86 (i>3)

Высокопроизводительный 32-х разрядный микропроцессор 80i86 ориентирован на эффективное выполнение программ в среде многозадачных ОС (типа Windows). Микропроцессор имеет 32-разрядные регистры и 32-х разрядные раздельные шины адреса и данных.

Физическое адресное пространство равно 4 Гб (232).

Виртуальное адресное пространство равно 64Тб (246).

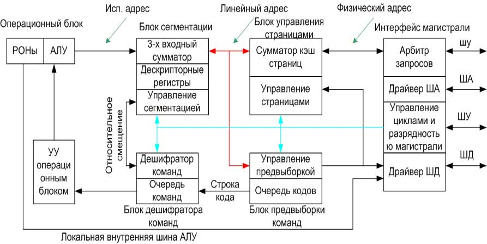

Структурная схема микропроцессора.

В состав микропроцессора входят:

- -операционный блок;

- -блок выборки команд;

- -диспетчер памяти;

- -устройство управления;

- -интерфейс магистрали.

Операционный блок вместе с устройством управления составляют центральный процессор микропроцессора, который предназначен для выполнения всех логических и математических операций. Операционный блок включает в свой состав АЛУ и восемь 32-хразрядных регистров (РОНов). Подсистема выборки команд реализует двухступенчатый алгоритм конвейеризации и состоит из блоков предвыборки команд и дешифрации команд. Блок предвыборки команд принимает команды из интерфейса магистрали, выстраивая их в очередь кодов.

Блок дешифрации команд производит преддешифрацию, то есть, определяет тип и формат команд, определяет номера используемых регистров, выделяет поле относительного смещения и передает его в блок сегментации для вычисления линейного адреса.

Диспетчер памяти состоит из блока сегментации и блока управления страницами, и осуществляет двухступенчатое формирование физического адреса ячейки памяти.

Имеется два режима работы микропроцессора:

- а)режим реальных адресов (реальный режим);

- б)режим защищенных виртуальных адресов (виртуальный режим).

В реальном режиме микропроцессор 80i86 работает как быстрый микропроцессор 8086. В реальном режиме страничная организация памяти не используется.

В защищенном режиме используются все возможности микропроцессора. При этом возможен многозадачный режим работы микропроцессора, причем каждая задача защищена и изолирована от других задач и от ОС. В защищенном режиме может быть реализована страничная организация виртуальной памяти объемом до 64 Тб для каждой задачи.

Оперативная память состоит из сегментов, каждый из которых может быть разбит на страницы. Каждая страница имеет фиксирующий размер по 4кб каждая страница, причем разбиение памяти на страницы возможно только в защищенном режиме.

Диспетчер памяти (и сегментный, и страничный) служат для вычисления физических адресов при обращении микропроцессора к памяти.

Интерфейс магистрали позволяет осуществить обмен микропроцессора информацией с ОЗУ и ПУ с помощью 32-хразрядной двунаправленной ШД, 34-хразрядной ША и 16-разрядной ШУ. Особенностью ШД является возможность динамического изменения ее разрядности. За один цикл шины может быть переданы 1,2 или 4 байта. По ША передаются 32-х адреса. ША состоит из 30 адресных линий, обозначенных как А31-А2 и 4-х линий выбора байт, обозначенных как ВЕ3-ВЕ0. Сигналы выбора байт определяют какие байты 32-хразрядной шины данных участвуют в текущем цикле обмена. Это позволяет легко согласовать ШД с байтной организацией памяти:

При ВЕ0=0. | Адресуется младший байт. | (т.е.D0-D7 ШД). | |

При ВЕ1=0. | Адресуется следующий байт. | (т.е.D8-D15 ШД). | |

При ВЕ2=0. | Адресуется следующий байт. | (т.е.D16-D23 ШД). | |

При ВЕ3=0. | Адресуется старший байт. | (т.е.D24-D31 ШД). | |

Регистры.

Набор регистров микропроцессора включает:

- -РОНы;

- -сегментные регистры;

- -указатели команд и регистр флагов;

- -регистры управления;

- -регистры адреса системы;

- -регистры отладки;

- -регистры тестирования.

Всего микропроцессор содержит 32 регистра, из которых 15 регистров могут адресоваться пользователем, кроме этого имеется указатель команд и 16 системных регистров недоступных пользователю. Все 16-тиразрядные регистры микропроцессоров 8086, 80 186, 80 286 содержатся в 32-разрядных регистрах микропроцессора 80i386.

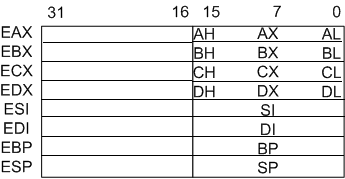

РОНы.

Восемь 32-хразрядных РОНов предназначены для хранения операндов и адресов, и располагаются в операционном блоке.

Младшие разряды РОНов (с 0 по 15) доступны отдельно при использовании имен AX, BX, CX, DX, SI, DI, BP, SP. При операциях с байтами для 4-х верхних регистров можно отдельно обращаться к младшему байту по, именам AL, BL, CL, DL и к старшим байтам по именам АН, ВН, СН, DH.

Верхние 4 регистра используются для хранения операнда и позволяют выполнять операции над отдельными байтами, 16-разрядными словами и 32-разрядными двойными словами. Остальные (4 нижних) регистра используются как адресные регистры для хранения 16-разрядных и 32-разрядных адресов.

Регистр ESP используется как указатель вершины стека.

EBP — используется как базовый регистр.

А регистры EDI и ESI используются как индексные регистры (для хранения индексов). В качестве базового и индексного регистров в некоторых случаях может использоваться и регистр данных EBX.

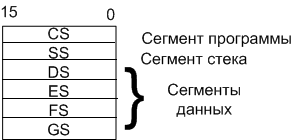

Регистры сегментов и дескрипторов сегментов.

Архитектура микропроцессора поддерживает организацию памяти в виде сегментов В реальном режиме: для хранения адресов начала соответствующих сегментов используется 16-хразрядные регистры CS, SS, DS, ES, FS, GS. Они выполняют те же функции, что и в микропроцессоре 8086. то есть, используются при вычислении физических адресов путем суммирования базового адреса, находящегося в сегментном регистре, со смещением. Такое суммирование выполняет блок сегментации, где располагаются и сами сегментные регистры. Максимальный размер сегмента в реальном режиме 64 Кбайт.

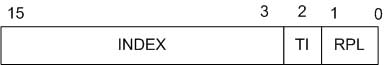

В защищенном режиме содержимое сегментного регистра используется как селектор сегмента. С каждым из сегментных регистров связан регистр дескриптора сегмента. Обращение к дескриптору осуществляется с помощью селектора, который представляет собой 16-хразрядный указатель, имеющий 3 поля.

Биты 0 и1 — это поле RPL, которое определяет уровень привилегий запроса и используется в механизме защиты памяти.

Бит 2 — Это поле TI, которое служит индикатором таблицы. При TI=0 используется глобальная таблица дескрипторов GDT. При TI=1 используется локальная таблица дескрипторов LDT.

Поле INDEX — служит индексом для выбора одного из 8192 дескрипторов (213), содержащихся в таблицах GDT или LDT. Сами 8-мибайтовые дескрипторы хранятся в памяти в составе массивов данных, сформированных в виде таблиц. В микропроцессоре используется 3 таблицы дескрипторов: GDT, LDT и таблица дескрипторов прерывания IDT.

С каждой из таблиц связан соответствующий регистр, который находится в микропроцессоре. Это регистры: GDTR, LDTR и IDTR.

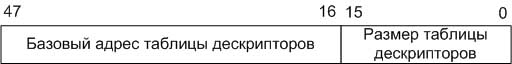

В качестве примера приведем формат регистра GDTR. Регистр GDTR 48-разрядный. 32-разряда задают базовый адрес таблицы дескрипторов, а 16 разрядов указывают размер этой таблицы в байтах.

При обращении селектора к таблице GDT сдвинутый на 3 разряда влево (умноженный на 8) селектор служит в качестве смещения для формирования адреса дескриптора. Это смещение сравнивается с границей (с размером) таблицы дескрипторов, находящейся в разрядах с 0 по 15 регистра GDTR. Если смещение превышает границу, то вырабатывается соответствующее прерывание. Если нарушения границы нет, то смещения суммируются с базовым адресом таблицы дескрипторов. В результате суммирования получается логический адрес младшего байта, выбираемого дескриптора.

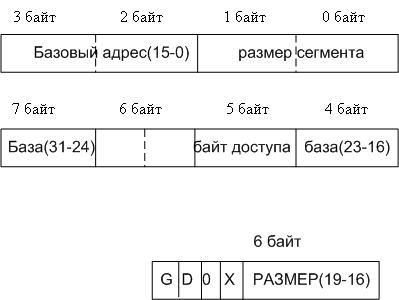

Выбираемый дескриптор имеет следующий формат.

32-хразрядный базовый адрес сегмента (база) и 20-тиразрядный размер сегмента размещены по частям в различных байтах дескриптора. Четыре бита 6-го байта определяют следующие атрибуты сегмента:

G — бит дробности, который указывает, в каких единицах задан размер сегмента;

При G = 0 — размер задан в байтах и максимальный объем сегмента в этом случае равен 220 = 1 Мб;

При G = 1 — размер задан в страницах, объемом 4 кб каждая страница. Максимальный объем сегмента в этом случае равен 212 х 220 = 232 = 4 Гб;

D — бит разрядности, который определяет разрядность формируемого относительного адреса или операнда.

При D = 0 — адрес или операнд — 16-тиразрядный;

При D = 1 — адрес или операнд — 32-хразрядный.

- 53-ий разряд — всегда = 0.

- 52-ой — имеет произвольное значение Х.

Байт доступа (5-ый) дескриптора определяет право доступа к выбираемому сегменту.