Алгоритмы выполнения микроопераций.

Микропрограммы

Если, то в четвертом такте выполняется сложение абсолютных значений слагаемых |A| и |B| с помощью сигналов Y4 и Y5. При этом по сигналу Y4 на входы сумматора SM подаются значения разрядов модуля В, и в сумматоре образуется сумма |A|+ |B|=S, которая по сигналу Y5 записывается в регистр RGA. Значение сигнала Р1 — переноса из старшего разряда сумматора запоминается в первом разряде регистра RGA (1… Читать ещё >

Алгоритмы выполнения микроопераций. Микропрограммы (реферат, курсовая, диплом, контрольная)

Основное назначение процессора — выполнение различных арифметических и логических операций. В качестве примера рассмотрим алгоритм выполнения операции сложения и вычитания чисел с фиксированной точкой в прямых кодах:

- 1. Сравнить знаки слагаемых, А и В. Если знаки различны, то вместо сложения выполнить операцию вычитания, а вместо вычитания — сложение. Если знаки одинаковые, то сложение остается сложением, а вычитание — вычитанием.

- 2. Если по результатам пункта 1 должно выполняться вычитание, то обратить код второго слагаемого В (т е получить обратный код от В)

- 3. Выполнить суммирование основных разрядов слагаемых, А и В без учета их знаков. Если идет вычитание, то при выполнении суммирования подать единицу на вход переноса младшего разряда сумматора, а полученному результату приписать знак первого слагаемого А.

- 4. Если идет вычитание, и в пункте 3 не был получен перенос из самого старшего разряда сумматора, то обратить код и знак результата (0 поменять на 1, а 1 — на 0)

- 5. Если выполнялся пункт 4, то вслед за этим пунктом добавить к полученному результату единицу младшего разряда.

Рассмотрим пример на выполнении операции вычитания (S=A-B):

А=0.111 011.

В=0.1 101.

S=A-B=A+(-B).

В соответствии с алгоритмом необходимо обратить код второго слагаемого В.

[B]обр=0.110 010.

А =0.111 011 A=0.111 011.

[B]обр=0.110 010 -B=0.1 101.

P1=1 0.101 101 0.101 110.

+ 1.

S=0.101 110.

Здесь Р1 — перенос из старшего разряда сумматора.

В соответствии с алгоритмом построим схему АЛУ и управляющего блока, а также микропрограмму для выполнения операции сложения-вычитания чисел в прямых кодах.

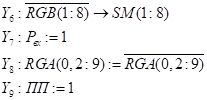

Список микроопераций:

(слагаемое А, поступающее по шине Х).

(суммирование без учета знака).

(в регистр, А записывается сумма, а перенос Р1 — в 1й разряд).

сигнал переполнения разрядной сетки В состав схемы входят:

- 1. восьмиразрядный комбинационный сумматор SM (1:8)

- 2. десятиразрядный регистр сумматора RGA (0:9)

- 3. девятиразрядный регистр второго слагаемого RGB (0:8)

- 4. Устройство управления (УУ), построенное в виде микропрограммного автомата Мили.

Комбинационный сумматор SM формирует восьмиразрядную сумму S, которая по сигналу Y5 поступает в регистр RGA. В дополнительном первом разряде регистра RGA (1) по тому же сигналу Y5 фиксируется значение сигнала переноса Р1. Нулевые разряды обоих регистров используются в качестве знаковых разрядов: при RGA (0)=0 число в регистре положительное, при RGA (0)=1 — отрицательное. Слагаемые, А и В загружаются в соответствующие регистры со входной шиной Х (0:8) по сигналам Y2 и Y3 соответственно. Значение суммы S записывается в регистр RGA и представляется на выходной шине Z (0:8) по сигналу Y10. Входы сумматора SM связаны с шинами передачи числа из регистра RGА в прямом коде, а из регистра RGB по сигналу Y4 модуль слагаемого В поступает в сумматор SM в прямом коде, а по сигналу Y6 — в обратном. По сигналу Y1 оба регистра обнуляются, а по сигналу Y7 на вход переноса младшего разряда сумматора SM поступает единица, т. е. По сигналу Y8 все разряды регистра RGA инвертируются. Если в сумматоре происходит переполнение, то УУ формирует сигнал переполнения разрядной сетки Y9.

В процессе выполнения операций сложения-вычитания чисел в схеме формируются следующие сигналы состояний:

— знаковый разряд первого регистра RGA, т е знак слагаемого А.

— знаковый разряд второго регистра RGВ, т е знак слагаемого В.

— сигнал переноса Р1 с выхода старшего разряда сумматора, который записывается в 1 м разряде регистра RGA.

— сумма по модулю два знаковых разрядов. Сигнал f=1, если знаки слагаемых, А и В различны, f=0, если знаки слагаемых, А и В одинаковы.

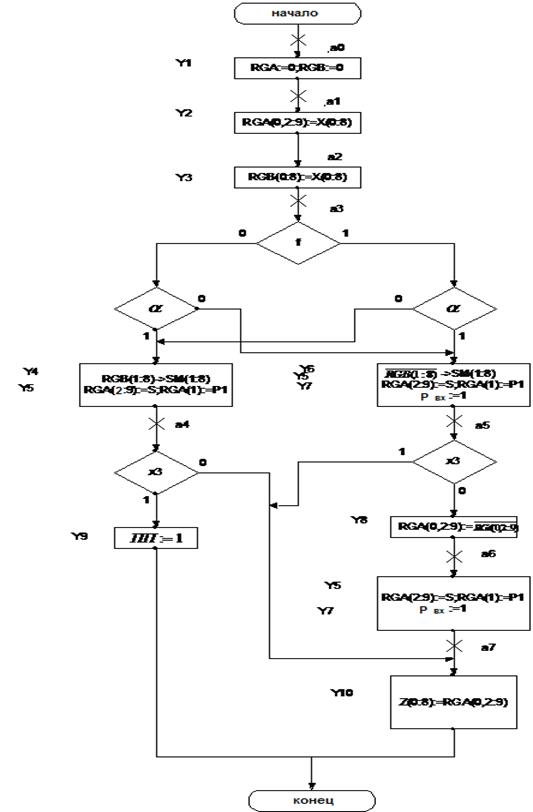

Сигналы Х3 и f поступают на входы УУ. УУ вырабатывает на своих выходах управляющие сигналы 10 микроопераций с Y1 по Y10. На входы УУ поступают также синхросигналы С и внешний сигнал б, который определяет вид выполняемой операции: если б=1, то выполняется операция сложения, если б=0, то выполняется операция вычитания. С учетом приведенных обозначений построим микропрограмму сложения-вычитания чисел в прямых кодах.

Выполнение микропрограммы начинается с подготовки регистров к приему слагаемых, А и В, для чего они обнуляются по сигналу У1. Сами слагаемые поочередно записываются в соответствующие регистры по сигналам Y2 и Y3. После этого по сигналу f анализируются знаки слагаемых, а по сигналу б определяется вид операции.

Если, то в четвертом такте выполняется сложение абсолютных значений слагаемых |A| и |B| с помощью сигналов Y4 и Y5. При этом по сигналу Y4 на входы сумматора SM подаются значения разрядов модуля В, и в сумматоре образуется сумма |A|+ |B|=S, которая по сигналу Y5 записывается в регистр RGA. Значение сигнала Р1 — переноса из старшего разряда сумматора запоминается в первом разряде регистра RGA (1), а значение знака слагаемого, А сохраняется в нулевом разряде регистра, А — RGA (0) и в дальнейшем используется в качестве знака суммы. Анализируется значение сигнала Х3:

- -Если Х3=0, т е перенос Р1=0, то значения знакового и основных разрядов суммы выдаются на выходную шину Z по сигналу У10 и операция сложения на этом завершается.

- -Если Х3=1 (был перенос Р1 из старшего разряда сумматора), то устройство управления формирует сигнал У9, извещающий о переполнении разрядной сетки. Это значит, что полученный результат не верен, и по сигналу У9 происходит прерывание программы процессора.

Если, то, начиная с четвертого такта, нужно выполнить следующую операцию над операндами, А и В: из большей абсолютной величины вычесть меньшую и полученному результату приписать знак большего по абсолютной величине операнда. Для этого в четвертом такте выполняется суммирование модуля, А с дополнением модуля В до единицы с помощью сигналов У5, У6, У7. При этом по сигналу У6 на входы сумматора подаются разряды модуля В в обратном коде, по сигналу У7 на вход переноса младшего разряда сумматора поступает единичный сигнал, а по сигналу У5 полученный результат |A|+1-|B| записывается в регистр RGA. Анализируется значение сигнала Х3:

Если Х3=1, т е был перенос Р1 из старшего разряда сумматора, то это значит, что полученный результат |A|+1-|B|1 или |A||В|, тогда в разрядах регистра RGA находится искомый результат |A|-|B|, поскольку произошло вычитание из большей абсолютной величины меньшей. При этом знак результата совпадает со знаком слагаемого А. В этом случае устройство управления в пятом такте сразу формирует сигнал выдачи результата У10 на шину Z и операция вычитания завершается.

Если Х3=0 (переноса Р1 не было), то |A|<|B| и в регистре RGA находится не сам искомый результат, а его дополнение до единицы, т е 1-(|B|-|A|) — дополнительный код разности. В этом случае производится коррекция результата, т е перевод результата из дополнительного кода в прямой. Для этого в пятом такте по сигналу У8 знаковый и основные разряды регистра RGA инвертируются, а в шестом такте по сигналам У7 и У5 к младшему разряду числа в RGA прибавляется единица. В седьмом такте полученный результат выставляется по сигналу У10 на шину Z и операция вычитания завершается.