Многоразрядные двоичные сумматоры

Сумматоры-вычитатели двоичных чисел. Схема 4-разрядного (с учетом знакового разряда) сумматора-вычитателя, содержащего четыре одноразрядных полных сумматора и четыре логических элемента исключающего ИЛИ, приведена на рис. 4.8. На входы сумматора-вычитателя поступают два двоичных числа, представленных 4-разрядными дополнительными кодами и, а также сигнал Z установки режима. Значение Z = 0… Читать ещё >

Многоразрядные двоичные сумматоры (реферат, курсовая, диплом, контрольная)

Сумматоры этого класса выполняют операцию сложения двух операндов, каждый из которых представляет собой n-разрядное двоичное число. Используют два типа сумматоров: сумматоры с последовательным и параллельным переносом.

Сумматоры с последовательным переносом

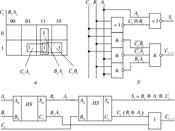

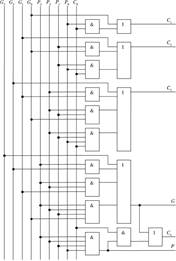

Для вычисления суммы двух n-разрядных двоичных чисел можно использовать неполные и полные одноразрядные сумматоры. На рис. 4.4, а, б приведены схема 4-разрядного сумматора и его условное обозначение. Схема составлена из четырех полных одноразрядных сумматоров SМ путем соединения.

Рис. 4.3. Минимизация структурой формулы для полного сумматора (а) и его логические схемы (б, в)

выхода переноса предыдущего одноразрядного сумматора с входом переноса последующего. Такой сумматор называется сумматором с последовательным переносом. Использование в нулевом разряде полного одноразрядного сумматора расширяет функциональные возможности 4-разрядного сумматора. Сумматор с последовательным переносом обладает низким быстродействием, поскольку сигналы суммы Sj.

Рис. 4.4. Схема 4-разрядного сумматора с последовательным переносом (а) и его условное обозначение (б)

и переноса С{ +, на выходе i-го одноразрядного сумматора появляются после того, как сформируется сигнал переноса в предыдущем (i — 1)-м одноразрядном сумматоре.

Сумматоры с параллельным переносом

Рассмотрим способ повышения быстродействия на примере 4-разряднго сумматора. Для этого запишем выходной сигнал переноса (4.3) в виде.

(4.5).

(4.5).

где

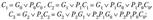

Из (4.5) следует, что:

- • сигнал G{ = 1 вырабатывается при наличии обоих сигналов в данном разряде (т.е. перенос происходит при Л; = В = 1), поэтому он называется функцией генерации переноса-,

- • сигнал Р. = 1 разрешает прохождение переноса С (. = 1 на выход, поэтому он называется функцией распространения переноса.

Используя (4.5), запишем выражения для сигналов переноса.

(4.6).

(4.6).

(4.7).

(4.7).

Выражения (4.6), (4.7) свидетельствуют о том, что для получения сигналов переноса +, (i = 0, 1, 2,3) достаточно располагать функциями Gv Р; (по сути, входными сигналами Ар Bj разрядов слагаемых) и сигналом внешнего переноса С0. Они описывают двухступенчатые комбинационные устройства, в первой ступени которых формируются логические произведения, а во второй — логические суммы. Поэтому можно считать, что сигналы всех переносов будут сформированы одновременно и за более короткий промежуток времени, чем в схеме многоразрядного сумматора с последовательным переносом. Рассмотренный способ формирования переносов называют параллельным, а сумматоры, построенные по этому способу, — сумматорами с параллельным переносом. Используя соотношения (4.6), (4.7), можно построить схему ускоренного (параллельного) переноса для 4-разрядного сумматора.

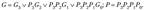

Путем соединения выводов переноса С0 и С4 4-разрядных сумматоров в последовательную цепь можно построить сумматоры с разрядностью 8, 12, 16 и т. д. Такой многоразрядный сумматор называют сумматором с последовательным групповым переносом. Для реализации параллельного группового переноса представим (4.7) в виде.

(4.8).

(4.8).

где.

(4.9).

(4.9).

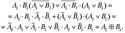

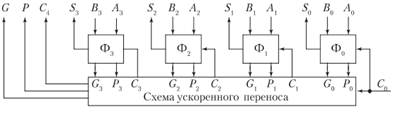

Так как выражения (4.8) и (4.5) имеют одинаковую структуру, параллельный групповой перенос между 4-разрядными сумматорами выполняется в соответствии с выражениями (4.6), (4.7), т. е. так же, как и параллельный перенос между отдельными разрядами каждого 4-разрядного сумматора. При этом в устройстве переноса для всех из них должны быть дополнительно сформированы сигналы (4.9). Схема ускоренного переноса, построенная с использованием формул (4.6), (4.7), (4.9), изображена на рис. 4.5.

Как видно из рис. 4.5, схема ускоренного переноса с помощью входных сигналов С0, Gr Р (г = 0, 1,2,3) формирует переносы в старшие разряды С (- С4, а также функции генерации G и распространения Р переносов, используемые при групповом включении 4-разрядных сумматоров. Формирование сигналов Gv Р. (i = 0, 1, 2, 3) и сигнала 5(. суммы двух одноразрядных двоичных чисел возлагается на формирователь. На рис. 4.6 представлен один из возможных вариантов схемы формирователя.

При построении этой схемы использовалось тождество.

Для его доказательства воспользуемся выражением (4.1) и формулами закона двойственности (3.15):

Структурная схема 4-разрядного сумматора с ускоренным переносом изображена на рис. 4.7. Сумматор содержит четыре одинаковых формирователя (Ф0, Ф1, Ф2, Ф3) отдельных разрядов суммы 5Р функций генерации G; и распространения Р{ переноса (см. рис. 4.6), а также схему ускоренного переноса (см. рис. 4.5), генерирующую помимо переносов С, — С4 функции генерации G и распространения Р для группового переноса.

Рис. 4.5. Схема ускоренного переноса.

Рис. 4.6. Схема формирователя.

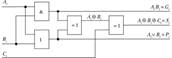

Сумматоры-вычитатели двоичных чисел. Схема 4-разрядного (с учетом знакового разряда) сумматора-вычитателя, содержащего четыре одноразрядных полных сумматора и четыре логических элемента исключающего ИЛИ, приведена на рис. 4.8. На входы сумматора-вычитателя поступают два двоичных числа, представленных 4-разрядными дополнительными кодами  и

и  , а также сигнал Z установки режима. Значение Z = 0 соответствует режиму сложения, a Z = 1 — режиму вычитания. С выхода сумматора-вычитателя снимается 4-разрядный дополнительный код результата

, а также сигнал Z установки режима. Значение Z = 0 соответствует режиму сложения, a Z = 1 — режиму вычитания. С выхода сумматора-вычитателя снимается 4-разрядный дополнительный код результата  , где

, где  — знаковый разряд. Выход переноса

— знаковый разряд. Выход переноса  одноразрядного сумматора

одноразрядного сумматора  не используется. Элементы исключающего ИЛИ предназначены для подачи на входы одноразрядных сумматоров разрядов В. в прямой (Z = 0) или инверсной (Z = 1) форме в соответствии с табл. 4.3.

не используется. Элементы исключающего ИЛИ предназначены для подачи на входы одноразрядных сумматоров разрядов В. в прямой (Z = 0) или инверсной (Z = 1) форме в соответствии с табл. 4.3.

Таблица 4.3

Входы. | Выходы. | ||

Z. | Bi |  | |

| |||

| |||

При Z = 0 на входах логических элементов исключающего ИЛИ действуют нулевые сигналы, поэтому сигналы разрядов Bt поступают на входы В. всех полных одноразрядных сумматоров без инверсии, на входе переноса Ct первого полного сумматора сигнал также равен нулю. Следовательно, происходит сложение двух операндов.

Рис. 4.7. Схема 4-разрядного сумматора с ускоренным переносом.

При Z= 1 логические элементы исключающего ИЛИ инвертируют сигналы разрядов В на входе переноса первого полного одноразрядного сумматора С{) = 1, благодаря чему образуется дополнительный код вычитаемого, поэтому выполняется операция вычитания.

Рис. 4.8. Схема сумматора-вычитателя.