Последовательный регистр.

Информатика

На первый триггер постоянно поданы сигналы J= О, K= 1, чтобы при считывании информации из регистра в триггеры записать нулевые сигналы. Прямой и инверсный выходы первого и второго триггеров подключены к J- и Х-входам второго и третьего триггеров. Прямой выход третьего триггера образует выход Y регистра. Входные сигналы X0, X1, X2 и сигнал записи C1 подаются на входы логических элементов, сигнал… Читать ещё >

Последовательный регистр. Информатика (реферат, курсовая, диплом, контрольная)

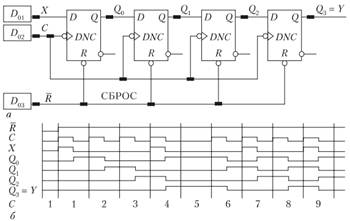

На рис. 13.15 изображена схема 4-разрядного последовательного регистра (а) и временные диаграммы (б) его работы. Регистр содержит:

- • четыре D-триггера, с занесением информации по срезу синхроимпульсов (при изменении логического уровня из 1 в 0);

- • три источника сигналов, из которых

используется для записи и считывания данных,

используется для записи и считывания данных,  - в качестве данных X,

- в качестве данных X,  - для формирования сигнала

- для формирования сигнала  сброса регистра.

сброса регистра.

В исходном состоянии (0-й такт) на асинхронные R-входы триггеров регистра поступает сигнал сброса  , поэтому выходные сигналы триггеров равны нулю.

, поэтому выходные сигналы триггеров равны нулю.

На последующих четырех тактах по срезу синхроимпульсов C в регистр заносится 4-разрядный операнд  , поступивший со стороны входа X. На 5-м такте регистр хранит занесенный операнд. На тактах с 6-го по 9-й осуществляется считывание содержимогорегистра. Первым на 6-м такте покидает регистр бит

, поступивший со стороны входа X. На 5-м такте регистр хранит занесенный операнд. На тактах с 6-го по 9-й осуществляется считывание содержимогорегистра. Первым на 6-м такте покидает регистр бит  , его место занимает бит Y = Q2 = 0 и т. д. Последним на 9-м такте покидает регистр бит Q0 = 1, хранящийся в первом триггере.

, его место занимает бит Y = Q2 = 0 и т. д. Последним на 9-м такте покидает регистр бит Q0 = 1, хранящийся в первом триггере.

Рис. 13.15. Схема 4-разрядного последовательного регистра на D-триггерах (а) и временные диаграммы (б), поясняющие принцип его работы

Параллельно-последовательный регистр

На рис. 13.16 изображена схема 3-разрядного регистра (о) и временные диаграммы (б), поясняющие принцип его работы. Регистр состоит из трех идентичных частей, каждая из которых содержит:

- • JK-триггер с асинхронными R- и 5-входами для предварительной установки;

- • два логических элемента 2И, подключенных к асинхронным входам по известной схеме D-триггера.

На первый триггер постоянно поданы сигналы J= О, K= 1, чтобы при считывании информации из регистра в триггеры записать нулевые сигналы. Прямой и инверсный выходы первого и второго триггеров подключены к J- и Х-входам второго и третьего триггеров. Прямой выход третьего триггера образует выход Y регистра. Входные сигналы X0, X1, X2 и сигнал записи C1 подаются на входы логических элементов, сигнал считывания C2 — на С-входы триггеров. Для записи данных используются асинхронные входы триггеров. Считывание осуществляется через информационные J- и X-входы.

В исходном состоянии при C1 = C2 = 0:

- • на входы триггеров подан 3-разрядный OnepaHflX2X1X0= = 101;

- • триггеры находятся в неопределенном состоянии, сигналы Q0-Q2 могут принимать любые значения.

Рис. 13.16. Схема 3-разрядного параллельнопоследовательного регистра на JK-триггерах (а) и временные диаграммы (б), поясняющие принцип его работы.

На 1-м такте подается строб записи C1 = 1 и по его фронту в триггеры записываются входные данные Q2QiQ0 = 101. На 2-м такте (при C1 = C2 = 0) состояние регистра соответствует режиму хранения. На 3-м, 5-м и 7-м тактах осуществляется считывание содержимого регистра по срезу импульсов C2= 1. Первым на 4-м такте покидает регистр бит Y= Q2= 1, его место занимает бит Y= Q1 = 0 и т. д. Последним на 8-м такте покидает регистр бит Q0 = 1, хранящийся в первом триггере. Триггеры регистра устанавливаются в состояние Q0 = Q1 = Q2 = 0.