Схемная реализация универсальных базисов «И-НЕ» и «ИЛИ-НЕ»

Запас по помехоустойчивости. Предполагаем, что «нуль» и «единица» на входах схемы создаются аналогичными каскадами, т. е. высокий уровень входного напряжения их ~ 5 В, а низкий уровень и°вх ~ 0,1 В. Тогда:• для логической «единицы» запас помехоустойчивости оценивается величиной 5' = и’ю — иатт = 5−2 = 3 (В); Напомним, что для надежного открытия диода (кремниевого) потенциал его анода должен быть… Читать ещё >

Схемная реализация универсальных базисов «И-НЕ» и «ИЛИ-НЕ» (реферат, курсовая, диплом, контрольная)

Схемы, выполняющие базисные логические операции «И-НЕ» и «ИЛИ-НЕ», строятся как на биполярных транзисторах, так и на полевых (МОП-транзисторах). Каждая из таких схем в качестве составных частей содержит инвертор (осуществляющий логическую операцию «НЕ») и элемент, на который возлагается логическое действие либо умножения («И»), либо сложения («ИЛИ).

В зависимости от используемых полупроводниковых элементов все многообразие логических схем делится на группы, которым присвоены специальные названия 112]:

- • диодно-транзисторная логика (ДТЛ);

- • транзисторно-транзисторная логика (ТТЛ);

- • транзисторно-транзисторная логика с диодами Шоттки (ТТЛШ);

- • МОП-логика («-МОП и р-МОП);

- • комплементарная МОП-логика (КМОП) и др.

Рассмотрим основные принципы схемного решения универсальных базисов «И-НЕ» и «ИЛИ-НЕ» на конкретных примерах.

Диодно-транзисторная логика

Главным признаком принадлежности элемента к ДТЛ является присутствие в его структуре инвертора на биполярном транзисторе и диодной схемы, выполняющей одну из логических операций: «И» (логическое умножение) либо «ИЛИ» (логическое сложение).

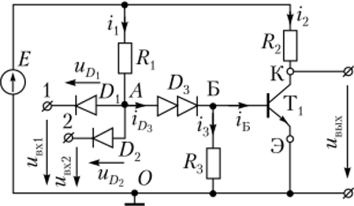

На рис. 19.8, а показана схема, которая в условиях позитивной логики осуществляет функцию «И-НЕ». Причем операция «И» возложена на диоды Dt и Dv а биполярный транзистор Т, включенный по схеме с ОЭ, работает как инвертор («НЕ»). Рассмотрим принцип действия цепи па рис. 19.8, а.

а.

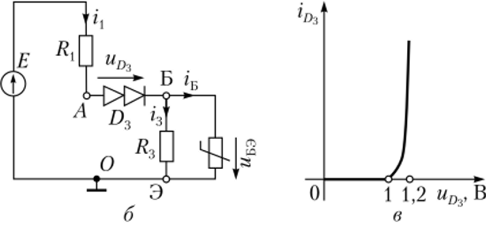

Рис. 19.8. Диодно-транзисторная логика:

а — схемное решение; 6 — эквивалентная схема для цепи база — эмиттер транзистора Т, в состоянии двух логических «единиц» на входе (логического «нуля» на выходе); в — расположение рабочей точки диода Ол на его ВАХ в режиме логической «единицы» на выходе Если закрыты оба входных диода Dx и D2 (а это возможно лишь при высоких уровнях входных напряжений и и[х2, когда потенциалы точек 1

и 2 выше потенциала точки А), источник ЭДС Е через двойной диод Д3 подает ток в базу транзистора Т, величиной гБ, достаточной для насыщения Tj. В этом случае имеем на выходе логический «нуль», т. е. у = 0.

Во всех остальных случаях, когда хотя бы одно из входных напряжений имеет низкий уровень, достаточный для открытия соответствующего диода (D, D2), ток, ответвляемый в D3, а значит, и в базу транзистора Т, падает практически до нуля. Т, переходит в режим отсечки. Использование в качестве Д3 двойного диода (эквивалент двум последовательным) обеспечивает более глубокую отсечку Т, за счет увеличения резистивного сопротивления участка, содержащего Д3, что весьма существенно в рассматриваемом режиме. Напряжение на выходе при закрытом Т, близко к Е. Следовательно, у = 1.

Таким образом, схема на рис. 19.8, а имеет следующие логические свойства:

• при хх = 1, х2 = 1 —5? у = 0;

хх = 0, х2 = 1,.

• при ' хх = 1, х2 = 0 —? у = 1,

хх = 0, х2 = 0.

Этот результат полностью совпадает с таблицей истинности логической функции «И-НЕ» (см. рис. 18.2).

Пример 19.1. Для цепи, изображенной на рис. 19.8, а, требуется:

- а) оценить величины напряжений на входах мвх1 и мвх2, необходимые для надежного обеспечения состояний логического «нуля» и логической «единицы» на выходе схемы;

- б) провести оценку запаса помехоустойчивости, предполагая, что входные напряжения мвх1 и мвх2 подаются от каскадов, идентичных рассматриваемому.

Параметры цепи принять следующими:

- 1) ?=5В;Д1 = 5 кОм; R2 = 2 кОм; R3 = 5 кОм;

- 2) Dp D2, D3 — кремниевые диоды. В открытом состоянии напряжение на D,

и D2 составляет ~0,6 В, а на D3—1,2 В;

- 3) для кремниевого транзистора, используемого в схеме, в «единичном» состоянии на выходе (режим отсечки) мвых = и'кэ " ?, а в «нулевом» состоянии ивых = и°кэ Е (транзистор глубоко насыщен), типичное значение и°кэ ~ 0,1 В.

- 4) напряжение на входе насыщенного транзистора Т, иБЭ ~ 0,6 В.

Решение

Рассмотрим отдельно каждый из статических режимов схемы на рис. 19.8, а.

1. Логический «нуль» на выходе (икэ = ивых ?; Т, — открыт). Это состояние имеет место при запертых диодах D, и D2, когда потенциалы точек 1 и 2 выше, чем потенциал точки Л (см. рис. 19.8, а), т. е. при высоком уровне мвх1 и мвх2 (две логические «единицы» на входе). Поэтому на эквивалентной схеме, представленной на рис. 19.8, б, диоды D, и D2 оборваны.

От источника питания Е через диод D3 и переход база — эмиттер транзистора Т, протекают токи прямого направления. Их величина должна быть достаточной для полного открытия D3 и создания режима насыщения в транзисторе Т,. Для эквивалентной схемы на рис. 19.8, б справедливо уравнение по второму закону Кирхгофа Е = i{Rt + uDi + иБЭ.

В рассматриваемом состоянии по условию задачи ~ 1,2 В, иБЭ ~ 0,6 В. Тогда потенциал точки Л в этом же режиме (рл = ф0 + иБЭ + и0ъ = 0,6 + 1,2 = 1,8 (В).

Следовательно, надежно запертое состояние входных диодов D, и D2 возможно только при мвх1 и мвх2, превышающих 1,8 В. Этот результат позволяет задать минимальный уровень напряжения логической «единицы» на входах цепи на рис. 19.8, а. С небольшим запасом возьмем wBxmin = 2 В.

2. Логическая «единица» на выходе (wBbIX * Е = 5 В; Т, в режиме отсечки). Данный режим возникает, когда хотя бы одно из входных напряжений (ивх1, ивх2) имеет низкий уровень. Закрытому состоянию транзистора Т, соответствует ток базы /Б ~ 0. Величина iB во многом зависит от сопротивления диода D3.

Резкого увеличения резистивного сопротивления D3 можно достигнуть, переместив его рабочую точку на начааьный участок его ВАХ (рис. 19.8, в), где ток через D3 пренебрежимо мал, уменьшив напряжение на нем до величины и0л < 1 В. Это условие равносильно требованию к величине потенциала точки Л в данном режиме, а следовательно, и к уровню входного напряжения. Действительно, при iB «0 потенциал (рБ = 0. Тогда uDi = <�рл — (рБ «срл < 1 В. При этом ток ix = = {Е- <�рл)//?, замыкается через любой из открытых диодов D, или D2 либо через оба.

Напомним, что для надежного открытия диода (кремниевого) потенциал его анода должен быть выше потенциала катода на величину порядка 0,6 В (см. условия задачи). Тогда для максимального уровня напряжения логического «нуля» на входе, например, при открытом диоде D, получаем мвх1 = Ф * - uDi < 1 — 0,6 = = 0,4 (В).

Таким образом, уровень логического «нуля» на входе нс должен превышать.

- 3. Запас по помехоустойчивости. Предполагаем, что «нуль» и «единица» на входах схемы создаются аналогичными каскадами, т. е. высокий уровень входного напряжения их ~ 5 В, а низкий уровень и°вх ~ 0,1 В. Тогда:

- • для логической «единицы» запас помехоустойчивости оценивается величиной 5' = и'ю — иатт = 5−2 = 3 (В);

- • для логического «нуля» запас помехоустойчивости определяется разностью напряжений 5° = мах тах — иах = 0,4 — 0,1 = 0,3 (В).