Фирма ST Microelectronics выпускает семейство микроконтроллеров STM32, которые выполнены на основе микропроцессорного ядра ARM Cortex-МЗ. Эти контроллеры считаются эталоном по балансу рабочих характеристик и стоимости. Они изначально ориентированы на применение в приборах с малым энергопотреблением и жесткими требованиями к характеристикам управления в режиме реального времени.

Организация внутренних шин

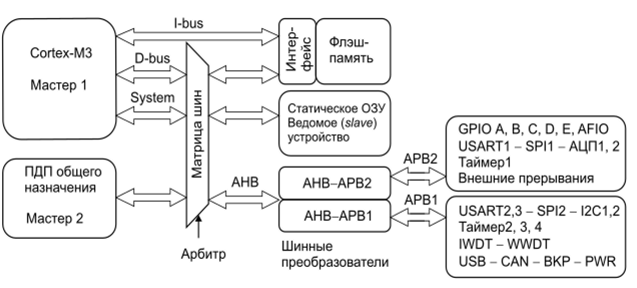

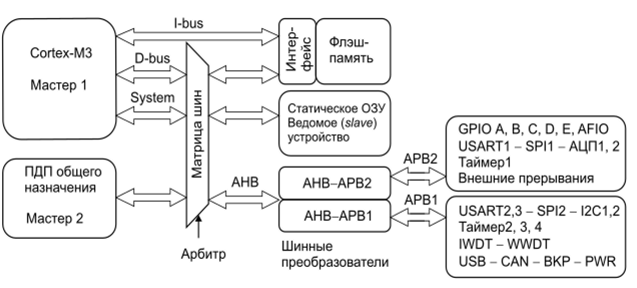

Микроконтроллеры STM32 выполнены на основе ядра Cortex-МЗ, которое подключено к флэш-памяти по отдельной шине инструкций (I-bus) (рис. 1.3). Поэтому обсудим лишь дополнительные детали, добавленные в STM32 к ядру Cortex-МЗ. Шина данных (D-bus) и системная шина (System) Cortex-МЗ подключены к матрице высокоскоростных шин (Advanced high-performance bus, АНВ). Внутреннее статическое ОЗУ (ведомое устройство, slave) подключено напрямую к матрице шин АНВ. с которой также связан блок ПДП. Подключение встроенных УВВ распределено между двумя периферийными шинами (Advanced peripheral bus, APB). Каждая из этих шин связана с матрицей шин АНВ посредством шинных формирователей. Матрица шин АНВ синхронизируется той же частотой, что и ядро Cortex-МЗ. Однако у шин АНВ имеются отдельные предделители, и поэтому в целях снижения энергопотребления их можно синхронизировать более низкими частотами. Важно обратить внимание, что шина АРВ2 может ра;

Рис. 1.3. Организация внутренних шин STM32.

ботать с максимальным быстродействием 72 МГц, а быстродействие шины APBI ограничено частотой 36 МГц (см. рис. 1.3).

Шина ЛРВ2 обслуживает следующие периферийные устройства:

- — порты I/O общего назначения (General purpose I/O, GPIO);

- — альтернативные функции портов I/O (Alternate function I/O, AFIO);

- — контроллеры последовательных интерфейсов (USART1 и SPI1);

- — контроллер аналого-цифровых преобразователей (ADC 1 и ADC2);

- — таймер-счетчик (ТС1);

- — внешние прерывания (EXTI).

Шина АРВ1 обслуживает следующие периферийные устройства:

- — контроллеры интерфейсов (USART2,3, SPI2,12C1,2);

- — таймеры-счетчики (ТС2, 3,4);

- -сторожевые таймеры -1WDT (независимый) и WWDT (оконный);

- — контроллеры последовательных интерфейсов (USB и CAN);

- — контроллер управления электропитанием (PWR);

- — регистры для резервного копирования данных (ВКР).

В качестве шинных мастеров могут выступать как CPU Cortex, так и блок ПДП. Благодаря свойственному матрице шин параллелизму, необходимость в арбитраже возникает только в случае попыток одновременного доступа обоих мастеров к статическому ОЗУ, шине АРВ1 или АРВ2. Тем не менее шинный арбитр гарантированно предоставляет 2/3 времени доступа для блока ПДП и 1/3 для CPU Cortex. В структуре внутренних шин предусмотрены отдельная шина инструкций и матрица шин, которая предоставляет несколько каналов передачи данных для CPU Cortex и блока ПДП.