Арифметические устройства.

Электротехника и электроника

Одним из направлений совершенствования КЦУ являлось создание микросхем с расширенными функциональными возможностями. Универсальным комбинационным узлом является арифметико-логическое устройство (АЛУ или ALU), которое реализует типовой набор арифметических и логических операций над многоразрядными двоичными числами. Параметры АЛУ (разрядность, быстродействие) и набор выполняемых операций зависят… Читать ещё >

Арифметические устройства. Электротехника и электроника (реферат, курсовая, диплом, контрольная)

Цифровые электронные средства обработки информации по существу выполняют с двоичными числами арифметические операции: сложение, вычитание, умножение, деление, а также сравнение, выделение большего, определение четности и др.

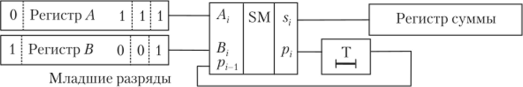

Сумматор представляет собой функциональный узел (блок), выполняющий сложение многоразрядных чисел. Многоразрядные сумматоры получают объединением одноразрядных сумматоров. Так, сумматор последовательного действия имеет простую структуру с единственным одноразрядным сумматором (рис. 13.3).

При этом слагаемые хранятся в w-разрядных регистрах, которые синхронно осуществляют их сдвиг. Получившееся значение суммы для соответствующего разряда заносится в выходной регистр результата, а значение переноса задерживается на один такт и подается на вход. Основным недостатком последовательного способа организации суммирования многоразрядных чисел является большое время выполнения операции.

Параллельный сумматор содержит п одноразрядных сумматоров (рис. 13.4), на входы которых разряды слагаемых подаются одновременно.

Разновидности параллельных сумматоров отличаются способами организации переноса. Последовательный перенос означает, что выход переноса рвых младшего разряда подключают непосред;

Рис. 133. Сумматор последовательного действия.

Рис. 13.4. Сумматор параллельного действия.

ственно к входу рвх следующего за ним старшего разряда. Быстродействие сумматора ограничено задержкой переноса, поскольку формирование сигнала переноса на выходе старшего разряда не может производиться до тех пор, пока сигнал переноса младшего разряда не распространится, но всей цепочке. Максимальное время сложения (распространения сигнала) будет ts = nt, где t — время задержки сигнала в одноразрядном сумматоре. Ускорение процесса сложения достигается за счет применения блока ускоренного переноса (комбинационной схемы). Для сложения чисел большой разрядности применяют наращивание разрядности, т. е. соединение сумматоров меньшей разрядности.

Операция вычитания в цифровой технике заменяется сложением уменьшаемого с вычитаемым, представленным в дополнительном коде. Для построения вычитателя используют сумматор с входными инверторами, преобразующим операнд В в обратный код.

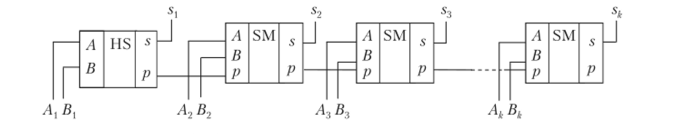

При обработке двоичных сигналов используются операции их сравнения и определения равнозначности кодов. Устройство, фиксирующее равенство двух операндов, называется цифровым компаратором. Равенство двоичных чисел А = {a"…aj…a} и В = = {b"…b…Ь) означает совпадение значений во всех разрядах. Идентичность разрядных операндов выявляется устройством, реализующим логическую операцию «равнозначность», выходной сигнал которого удовлетворяет соотношениям у = 1 при а = b и у = 0 при а ^ Ь. Аналогичный результат можно получить, если использовать инвертированный выходной сигнал широко распространенного устройства «исключающее ИЛИ», образующего сумму по модулю 2 (рис. 13.5, а).

Для определения равенства многоразрядных операндов необходимо выходы всех схем равнозначности, фиксирующих равенство значений разрядов, подключить к входу схемы И. Приведенное устройство регистрирует лишь равенство или различие двух чисел. В ряде приложений требуется выделить большее число. Сопоставление двоичных чисел производится по разрядам с учетом того, что вес любого старшего разряда больше веса младшего. Для выявления большего одноразрядного числа используется дополнительный выход ср. Объединение двух элементов с помощью логиче;

а б в.

Рис. 13.5. Схема сравнения одноразрядных чисел (а), устройство сравнения двухразрядных чисел (б), цифровой компаратор (в)

ской схемы приводит к блоку двухразрядного устройства сравнения (рис. 13.5, б), выполняемого в виде отдельного блока (рис. 13.5, в). Для наращивания разрядности сравниваемых чисел применяют каскадное или пирамидальное соединение нескольких компараторов.

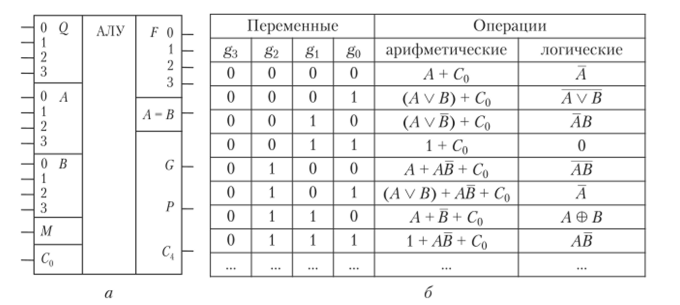

Одним из направлений совершенствования КЦУ являлось создание микросхем с расширенными функциональными возможностями. Универсальным комбинационным узлом является арифметико-логическое устройство (АЛУ или ALU), которое реализует типовой набор арифметических и логических операций над многоразрядными двоичными числами. Параметры АЛУ (разрядность, быстродействие) и набор выполняемых операций зависят от областей применения, на основе которых формулируются технические требования. Типичным вариантом является АЛУ, выпускаемое в виде завершенной ИМС и реализующее полный набор логических функций двух переменных и 16 арифметических действий с двумя четырехразрядными числами (рис. 13.6, а).

Микросхема имеет восемь входов для ввода двух чисел — А и В, четыре выхода для представления результата преобразования F, входы управляющих сигналов Q и кода характера выполняемой операции М. При М = 0 производятся арифметические действия.

Рис. 13.6. АЛУ (я) и выполняемые операции (б).

с операндами, а при М = 1 выполняется одна из логических операций (рис. 13.6,6). Вид осуществляемой операции определяется четырехразрядным кодом <7з<72<71 <7о t устанавливаемым на управляющем входе.

Для выполнения действий с числами большей разрядности используется соединение секций из нескольких АЛУ. Для этого в ИМС предусмотрен вход переноса С0 и выходы G, Р, С4 для организации взаимодействия с блоком ускоренного переноса при наращивании разрядности.

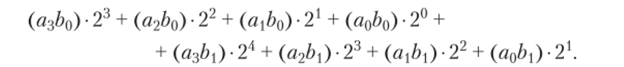

Умножение многоразрядных двоичных чисел, служащее одной из основных операций цифровой обработки данных, содержит множество поразрядных арифметических действий и сдвигов результатов. Например, схема умножения четырехразрядного А = = а3- 23 + а2-22 + а{ -21 + я0— 26 и двухразрядного В = b{ -21 + Ь0-2° чисел содержит операции перемножения двоичных разрядов и сложения частичных произведений со сдвигом.

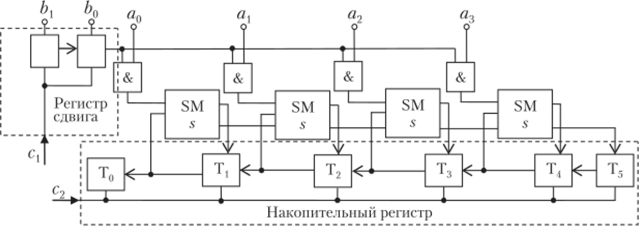

Выполнение умножения занимает п тактов, что равно количеству разрядов множителя. Для осуществления сдвигов используются регистр сдвига, содержащий разряды множителя, и накопительный регистр, сохраняющий результаты частичных произведений (рис. 13.7).

На каждом такте по синхроимпульсу сх разряды множителя b^ последовательно поступают па вентили И (&), выполняющие операцию перемножения разрядов множимого на разряд множителя: cij-bk (j = 0,…, т — 1), где т — число разрядов множимого. При b* = 1 на входы одноразрядных сумматоров с выходов схемы совпадения поступают значения разрядов множимого, а при Ь^ = 0 — нулевые значения. После окончания операции сложения и занесения результатов в накопительный регистр под действием синхроимпуль;

Рис. 13.7. Схема умножителя последовательного действия са С2 происходит сдвиг результата на один разряд влево с помощью элементов сдвига Т (задержки сигнала на такт). В результате циклического повторения указанных операций в накопительном регистре образуется произведение. Время выполнения умножения определяется разрядностями сомножителей и временем распространения переноса через сумматоры: Гумн ~ mn tp.

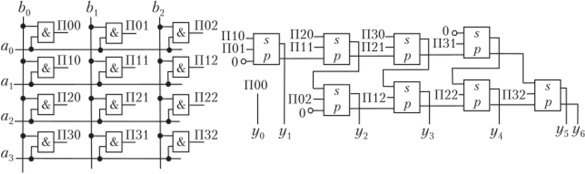

Вследствие зависимости производительности вычислительного устройства от быстродействия умножителей разработаны аппаратные средства, осуществляющие операцию умножения за один такт. Наиболее распространены матричные структуры, содержащие одноразрядные сумматоры и схемы совпадения (рис. 13.8).

Рис. 13.8. Схема матричного умножителя.

Параллелизм выполнения операций в матричном умножителе позволяет исключить элементы хранения промежуточных результатов. Матрица логических элементов И, входы которых соединены с шинами множимого и множителя, формирует частичные произведения Щ = afik, которые затем суммируются.

Регулярность структуры устройства обеспечивает большую плотность упаковки элементов. Преобразование логики выполнения операций позволило разработать схемы быстрых умножителей.