Структура и описание триггерных систем

Триггерная система, обычно называемая триггером определенного типа (например, задержки), состоит из одной или нескольких триггерных ячеек, объединенных посредством комбинационных схем (КС). Триггерная ячейка, базирующаяся на элементе памяти, имеет единственную внутреннюю переменную г = Q, принимающую два возможных значения: 0 и 1. Выходная величина совпадает с переменной состояния у = Q. Как… Читать ещё >

Структура и описание триггерных систем (реферат, курсовая, диплом, контрольная)

Триггерная система, обычно называемая триггером определенного типа (например, задержки), состоит из одной или нескольких триггерных ячеек, объединенных посредством комбинационных схем (КС). Триггерная ячейка, базирующаяся на элементе памяти, имеет единственную внутреннюю переменную г = Q, принимающую два возможных значения: 0 и 1. Выходная величина совпадает с переменной состояния у = Q. Как правило, триггер имеет взаимно дополняющие выходы: прямой Qw инверсный^. Входные управляющие сигналы разделяют по выполняемой ими роли на информационные (логические), подготовительные (разрешающие), исполнительные (командные).

Тип триггера определяется его логическим уравнением, получаемым из таблицы состояний, которая содержит значения выходного сигнала Q(, z+1) в (п + 1)-м такте в зависимости от информационных сигналов Х(«>

и предшествующего состояния Для обозначения типа триггера используют наименования информационных входов RS, JK, Г, D.

Общее количество различных 'григгеров, которые могут быть реализованы с р входами, определяется формулой т = 51р> т. е. число одновходовых триггеров тл = 25, двухвходовых т2 = 625. На практике используется ограниченное количество типовых потенциальных триггеров, отличающихся выполняемой функцией, аппаратными затратами, быстродействием, функциональной надежностью. Наиболее распространенными являются универсальные/К-триггеры, D-триггеры задержки, '/'-триггеры со счетным входом и тактируемые RST-три ггсры.

Общие параметры триггера (уровни напряжений и токов единичного и нулевого уровней, коэффициент объединения по входу, коэффициент разветвления по выходу, потребляемая мощность) совпадают с параметрами логических элементов, образующих его схему. К характерным параметрам триггеров относят: число однотипных ЛЭ в реализации; время переключения или максимальную частоту переключений; требования к уровню, длительности и фронтам синхроимпульса.

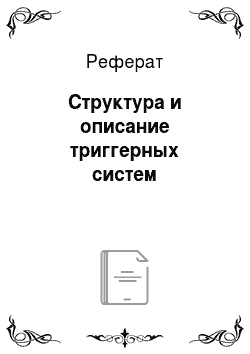

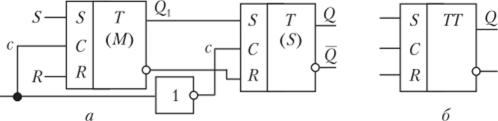

Одноступечатая триггерная система содержит элемент памяти (асинхронный RS-триггер), в котором с помощью комбинационной схемы образованы внутренние контуры (рис. 14.2, а).

Рис. 14.2. Общая структура триггера (а) и таблица переходов //Л'-триггера (б).

Преобразование полученной ранее логической формулы.

приводит ее к форме Q" +1 = 5 v RQ" , и можно записать сокращенную таблицу состояний триггера (рис. 14.2, б).

Переключение асинхронного триггера (установка или сброс) начинается непосредственно в момент поступления входного информационного сигнала, а заданный уровень выходного сигнала устанавливается спустя интервал переключения /пер, в течение которого наблюдается переходный процесс с неопределенным уровнем сигнала. В цепочке триггеров ложный сигнал может накапливаться и приводить к ошибкам функционирования устройства.

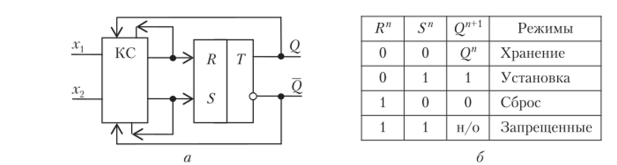

Для исключения ложного срабатывания применяют синхронное (одновременное) переключение всех триггеров после завершения переходных процессов. Это обеспечивается посредством введения разрешающего (стробирующего) импульса, который задает такт работы устройства. Синхронный //5-триггер (RST) состоит из базового асинхронного триггера, а также комбинационной схемы из двух логических элементов И (рис. 14.3, а).

Рис. 14.3. Структура синхронного ЛУ-триггера (а), таблица переходов (б), форма синхроимпульса (в) и условное обозначение (г).

Сигналы на информационных входах устанавливаются до подачи синхроимпульса. При любых наборах информационных сигналов и нулевом синхросигнале (с = 0) на входах асинхронного ЙЛ'-триггсра Rj = 0, 5, = 0 и триггер находится в режиме хранения (рис. 14.3, б). Установка с = 1 приводит к работе устройства как базового асинхронного ЛУ-трштора. Триггер срабатывает при достижении тактирующим сигналом уровня переключения Un логических элементов (рис. 14.3, в). Активное состояние информационных входов триггера (рис. 14.3, г) будет в интервале tc.

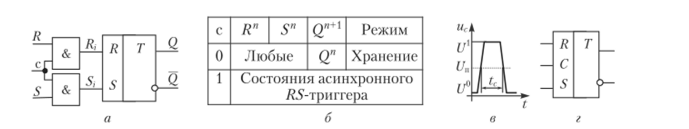

Из триггеров с одним информационным входом распространен D-триггер {Delay), в котором сигнал Q" +1 на выходе повторяет входной сигнал предшествующего интервала (рис. 14.4, а).

Тактируемый D-триггер можно получить на основе синхронного ЛУУ-триггера {RST), если сигнал D подать на его установочный вход S и через инвертор на вход сброса R (рис. 14.4, б). При изменении входа D в такте п состояния, например с U0 на Й1, до прихода синхроимпульса на выходе сохраняется предшествующее состояние Q" = 0, так как информационные входы RST не активизированы (рис. 14.4, в). Выходной сигнал изменится с задержкой.задаваемой тактирующим импульсом, и сохранится в (и+1)-м такте. Таким образом, триггер выполняет задержку (запоминание) разряда двоичного числа на интервал tD. В микросхемах D-триггеров обычно предусмотрены установочные входы для предварительной установки всех ячеек в нулевое или единичное состояние (рис. 14.4, г).

В одноступенчатых триггерах записываемая информация появляется па выходе с задержкой, зависящей от переходных процессов.

Рис. 14.4. Состояния D-триггера (а), структура (б), временные диаграммы (в) и условное обозначение (г) во всей цепи прохождения сигнала. Функционирование ряда цифровых устройств требует получения числовых данных в четко определенные моменты времени. Для этого разработаны двухступенчатые триггеры, производящие разделение процессов записи и воспроизведения информации. Триггер с двухтактным управлением можно реализовать в виде каскадного соединения тактируемых /бУ-триггеров, причем на первый триггер сигнал синхронизации поступает непосредственно, а на второй — через инвертор (рис. 14.5, а).

Рис. 14.5. Двухступенчатый триггер (а) и его обозначение (б).

В приведенной структуре реализован принцип разделения во времени записи и хранения данных, причем запись сигнала в ведущий (Master) триггер осуществляется в момент начала синхроимпульса с (по фронту), а перезапись в ведомый (Slave) — в момент окончания синхроимпульса (по срезу). До прихода тактового импульса (с = 0) ведущий триггер Т (М) находится в режиме хранения <2] = Qf. С приходом тактового импульса при с = 1 входы ведущего триггера активизируются и в запоминающий элемент заносятся поданные на вход данные. Входы ведомого триггера в это время блокированы сигналом синхронизации низкого уровня, поступающим через инвертор. С прекращением тактового импульса запираются входы ведущего триггера и активизируются входы ведомого T (S). В его запоминающую ячейку заносятся данные, принятые ведущим триггером. Назначение триггера определяется структурой первой ступени, а двухступенчатость отражена в обозначении 7 Т (рис. 14.5, б).

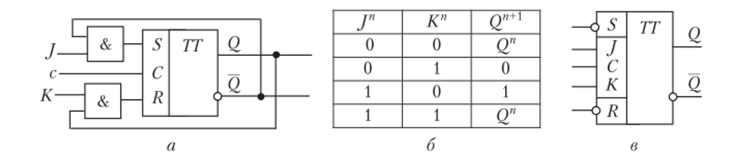

Универсальным является //^-триггер, который может быть реализован на основе двухступенчатого /?5-триггера с использованием комбинационной схемы, осуществляющей связь выходов с входами (рис. 14.6, а).

Включение элементов ИЛИ в цепи связи позволило организовать входы/ (Jump — переброс) и К (Keep — удержание), а также устранить неопределенность в состояниях базового Л5-триггера. При поступлении на вход комбинацииJ =1, К =1 на выходе устанавливается состояние, противоположное предшествующему (рис. 14.6, б). В соответствии с таблицей состояний функционирование/К-триггера описывает логическая формула Qn+i =J" Q" V K" Q" . Для расширения возможностей построения схем на ИМС/К-триггеров.

Рис. 14.6. Структура JTf-триггера («), таблица переходов (б) и обозначение (в).

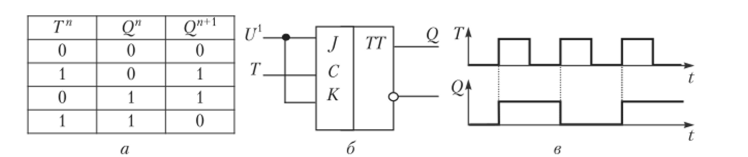

(рис. 14.6, в) в нем предусмотрены установочные входы и дополнительные элементы на входе (схемы И, ИЛИ). На основе универсального /ТС-триггера с помощью внешних соединений можно реализовать другие распространенные типы триггерных систем, например применяемый в пересчетных устройствах триггер со счетным входом (Г-триггер), изменяющий свое состояние на противоположное при поступлении единичного сигнала на вход Т (рис. 14.7, а).

В соответствии^таблицей состояний имеем логическую формулу Q" +1 = TQ" V Т (У сопоставление которой с формулой/ТС-триггера показывает, что счетный триггер реализуется при подаче единичных сигналов на информационные входы (рис. 14.7, б). Изменение состояния Г-триггера происходит при переходе входного сигнала с нулевого на единичный уровень (рис. 14.7, в).

Рис. 14.7. Состояния счетного триггера (а), структура (б), временные диаграммы (в) Промышленность выпускаетJK-, RS- и 7'-триггеры в виде завершенных ИМ С, содержащих два или четыре прибора с дополнительными входами и комбинационными схемами И, ИЛИ в одном корпусе. Многие ИМС комбинационных устройств (мультиплексоров, преобразователей кодов, сумматоров) на кристалле имеют триггеры для возможности хранения промежуточных результатов.