Сумматоры.

Основы функционирования систем сервиса. В 2 ч. Часть 2

Существенным недостатком сумматоров с последовательным переносом является трудность достижения высокого быстродействия, связанной с тем, что процесс распространения переноса носит последовательный характер. Для повышения быстродействия параллельного сумматора используется специальный блок ускоренного переноса. При этом формирование переносов производится одновременно для всех разрядов. Сумматоры… Читать ещё >

Сумматоры. Основы функционирования систем сервиса. В 2 ч. Часть 2 (реферат, курсовая, диплом, контрольная)

Комбинационные устройства, которые рассматривались выше, выполняют логические функции. Для описания их работы используется аппарат алгебры логики. Входные и выходные сигналы высокого и низкого уровня представляются соответственно как лог.1 и лог.О.

Дискретная техника представлена и другим классом устройств, назначение которых состоит в выполнении арифметических действий с двоичными числами.

Особенность арифметических устройств состоит в том, что сигналам приписываются не логические, а арифметические значения 1 и 0 и действия над ними подчиняются законам двоичной арифметики. Для описания их работы также удобно пользоваться таблицами истинности.

Важнейшая из арифметических операций — сложение (суммирование). Помимо прямого назначения она используется и при других операциях: вычитание — это сложение, в котором вычитаемое вводится дополнительном коде, а умножение и деление — это последовательное сложение и вычитание.

Сумматором (англ. Adder) называется комбинационное устройство, предназначенное для арифметического сложения двух двоичных чисел.

Сумматор является основным узлом арифметико-логического устройства любого процессора.

Классификация. По количеству одновременно обрабатываемых разрядов сумматоры подразделяются на одноразрядные и многоразрядные.

По числу входов и выходов одноразрядные сумматоры делятся:

- • на четвертьсумматоры;

- • полусумматоры;

- • полные одноразрядные двоичные сумматоры.

По способу представления и обработки данных многоразрядные сумматоры подразделяются:

- • на параллельные, в которых слагаемые складываются одновременно по всем разрядам, и для каждого разряда имеется свое оборудование;

- • последовательные, в которых обработка данных ведется поочередно, разряд за разрядом на одном и том же оборудовании.

По способу организации межразрядных переносов параллельные сумматоры подразделяются на сумматоры:

- • с последовательным переносом;

- • с параллельным переносом;

- • с групповой структурой;

- • со специальной организацией цепей переноса.

По способу выполнения операции сложения и возможности сохранения результата сложения можно выделить два основных вида сумматоров:

- • комбинационный, выполняющий микрооперацию S = А + В, в котором результат выдается по мере его образования (это комбинационная схема в общепринятом смысле слова);

- • накапливающий, выполняющий микрооперацию S = S + А, в котором результат сложения запоминается.

В зависимости от системы счисления различают двоичные и двоично-десятичные сумматоры.

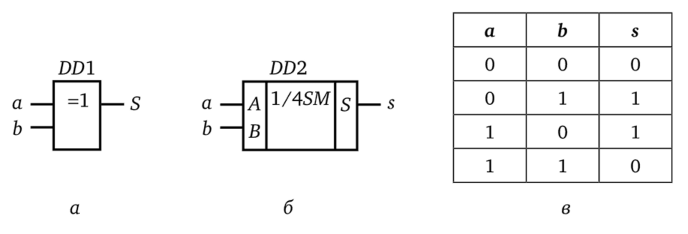

Одноразрядные двоичные сумматоры. Простейшим сумматором является четвертьсумматор, имеющий два входа, А и В, на которые подаются одноразрядные числа, и один выход S (Sum), на котором реализуется арифметическая сумма в данном разряде. Четвертьсумматор представляет собой ЛЭ «Исключающее ИЛИ».

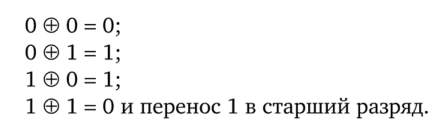

Логическое уравнение четвертьсумматора имеет вид.

где 5 — сумма; а и Ь — одноразрядные двоичные числа; Ф — символ операции сложение по модулю два или логической операции «Исключающее ИЛИ».

Сложение двух одноразрядных двоичных чисел производится следующим образом:

Логическая схема, условное обозначение и таблица истинности четвертьсумматора приведены на рис. 11.21.

Рис. 7 7.27. Четвертьсумматор:

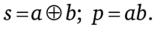

а — логическая схема; б — условное обозначение; в — таблица истинности Схема полусумматора имеет два входа, А и В, на которые подаются одноразрядные числа, и двух выходов: на одном S реализуется арифметическая сумма в данном разряде, а на другом С (Carry) — перенос в следующий (старший) разряд.

Для обозначения полусумматора служат буквы HS (half sum — полусумма). Его условное графическое обозначение, таблица истинности и схема полусумматора приведены на рис. 11.22.

Логические уравнения полусумматора для суммы и для сигнала переноса имеют вид.

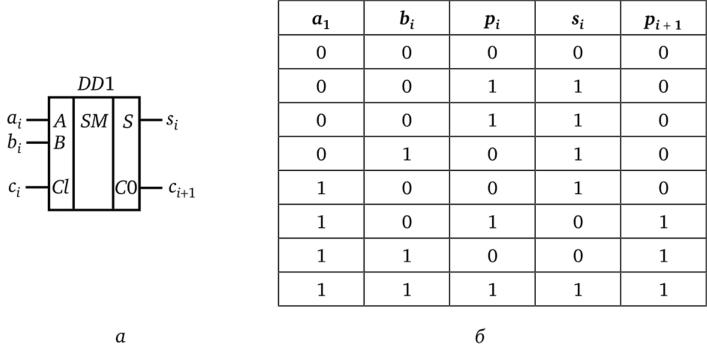

Одноразрядный полный сумматор имеет три входа А, В и Cl (Carry Input) для подачи цифр разрядов слагаемых аг, bt и переноса cf и два выхода S и СО (Carry Output), на которых соответственно формируются сумма Sj и перенос pi+1, предназначенный для передачи в следующий разряд.

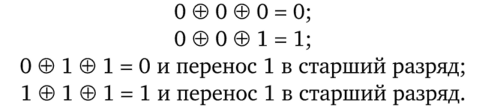

Сложение трех одноразрядных двоичных чисел производится следующим образом:

Условное обозначение и таблица истинности полного сумматора приведены на рис. 11.23.

Рис. 11.22. Полусумматор:

a — логическая схема; б — условное обозначение; в — таблица истинности.

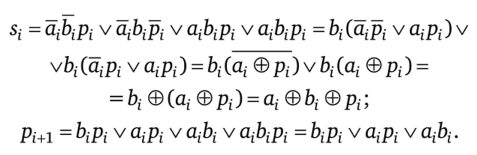

Рис. 11.23. Условное обозначение (а) и таблица истинности (б) полного сумматора Исходя из таблицы истинности, принцип работы сумматора описывается следующими логическими выражениями:

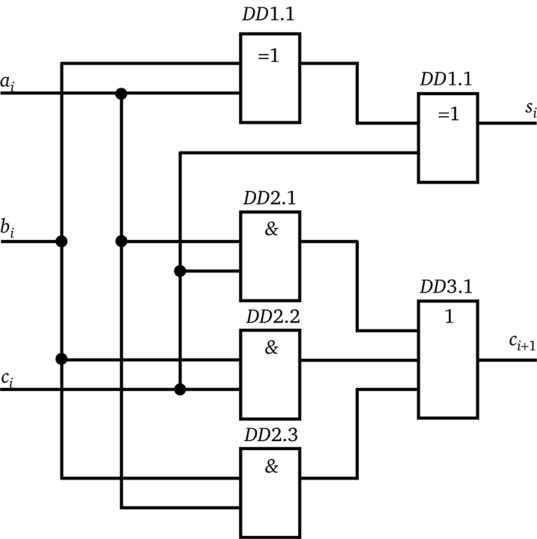

По полученным логическим уравнениям составляем схему одноразрядного полного сумматора, приведенную на рис. 11.24.

Одноразрядные сумматоры используются для построения многоразрядных.

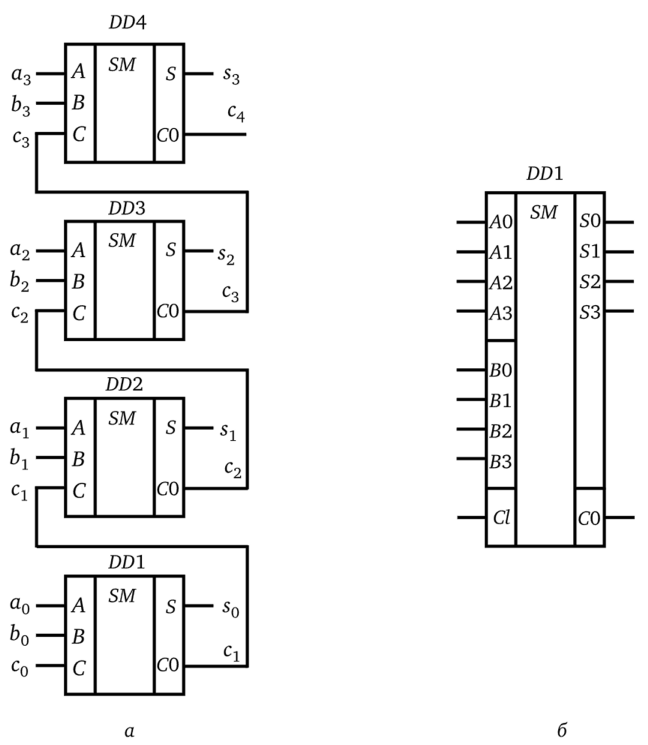

Четырехразрядный двоичный сумматор. На рис. 11.25, а приведена схема четырехразрядного параллельного полного двоичного сумматора с последовательным переносом.

Рис. 11.24. Логическая схема одноразрядного полного сумматора.

Сумматор состоит из четырех параллельно включенных одноразрядных сумматоров DD1…DD4, у которых вход переноса CI последующего сумматора соединен с выходом переноса СО предыдущего.

Цифры разрядов слагаемых а3…а0 и Ь3…Ь0 поступают на соответствующие одноразрядные сумматоры. Каждый из сумматоров формирует на своих выходах сумму s и перенос с, передаваемый на вход сумматора следующего, более старшего разряда.

Существенным недостатком сумматоров с последовательным переносом является трудность достижения высокого быстродействия, связанной с тем, что процесс распространения переноса носит последовательный характер. Для повышения быстродействия параллельного сумматора используется специальный блок ускоренного переноса. При этом формирование переносов производится одновременно для всех разрядов. Сумматоры с блоками ускоренного переноса относятся к разряду сумматоров с групповой структурой, которые используют ускоренные переносы на различных уровнях сумматора, т. е. в группах и между ними.

Сумматоры выпускаются в виде ИМС нескольких серий. Например, параллельный четырехразрядный полный двоичный сумматор К561ИМ1, условное обозначение которого приведено на рис. 11.25, б.

На основе двоичных сумматоров строятся десятичные сумматоры, предназначенью для суммирования двоично-десятичных чисел.

Рис. 11.25. Четырехразрядный полный двоичный сумматор:

а — схема; б — условное обозначение Сумматор может вычислять не только сумму, но и разность двух двоичных чисел. Для этого вычитаемое необходимо представить в виде отрицательного двоичного числа в дополнительном коде.

Сумматоры являются неотъемлемой частью арифметико-логических устройств, которые являются ядром любого микропроцессора.