Разработка функциональной схемы кодера

В схему кодера входят такие функциональные блоки, как:

- — КРИ 1/3;

- — ФПСк;

- — КОИ 4/1;

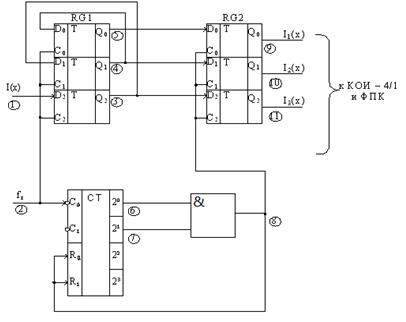

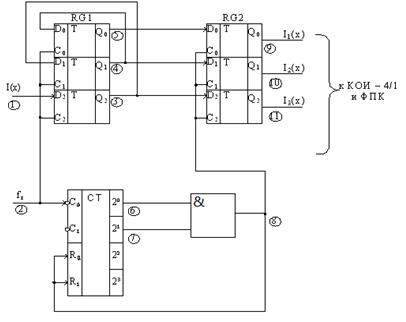

Наиболее простым способом построения КРИ 1/3 является использование двух регистров RG (последовательного RG1 и параллельного RG2) и блока формирования тактовых частот RG1 и RG2, представляющих собой схему управления, построенную на кольцевом счётчике CT и дизъюнкторе. Последовательный и параллельный регистры RG содержат по k0 ячеек памяти, т. е. в нашем случае по три ячейки памяти. Регистры представляют собой совокупность k0 D-триггеров, т. е. нам необходимо k0=3 D-триггера. Функциональная электрическая схема КРИ — 1/3 представлена на рисунке 4.1.

Рисунок 4.1 — Функциональная электрическая схема КРИ 1/3 кодера.

Для описания принципа работы КРИ будем использовать временные диаграммы, построенные для контрольных точек (рисунок 4.2).

Отметим, что при построении временных диаграмм, необходимо учесть то, что счётчик работает по отрицательному фронту (по спаду), а данные считываются по переднему фронту тактовой последовательности.

Рисунок 4.2 — Временные диаграммы работы КРИ 1/3.

Функциональная электрическая схема ФПСк выполняется в виде схем умножения полиномов и реализуется в виде регистра сдвига RG либо со встроенными сумматорами по модулю два.

Для полиномов.

g (x)=1+x3+x15+x19, g (x)=1+x8+x17+x18, g=1+x6+x11+x13

построим ФПСк:

Так как максимальная степень порождающих полиномов m=19, RG будет содержать 19 сумматоров по модулю два.

Рисунок 4.3 — Схема функциональная электрическая ФПСк.

Нумерация ячеек памяти ФПСк ведётся справа налево. Места включения сумматоров по модулю два определяются ненулевыми членами порождающих полиномов; выходной сумматор по модулю два является многовходовым (3 входа).

КОИ — 4/1 кодера ССК выполняется в виде синхронного мультиплексора на соответствующее число информационных и управляющих входов, а также формирователя сигналов управления мультиплексором, представляющего собой двоичный счётчик.