ОЗУ для временного хранения информации

Перед началом работы необходимо сбросить счетчики в нуль сигналом «Сброс». При отсутствии операций записи и чтения память находится в состоянии чтения (сигналWR равен единице), а на адресные входы памяти подается код адреса записи со счетчика записи. При подаче строба записи «-Зап.» производится запись входных данных по адресу из счетчика записи. Входные (записываемые) данные должны выставляться… Читать ещё >

ОЗУ для временного хранения информации (реферат, курсовая, диплом, контрольная)

Главное применение микросхем оперативной памяти, непосредственно следующее из ее названия, — это временное хранение цифровой информации, всевозможных массивов кодов, таблиц данных, одиночных чисел и т. д. Цель такого хранения информации состоит в том, чтобы в любой момент иметь возможность быстро ее прочитать для дальнейшей обработки, записи в энергонезависимую память (в ПЗУ, на магнитные носители) или для другого использования. Записанная в оперативную память и непрочитанная затем информация не имеет смысла, так как при выключении питания она безвозвратно пропадет.

Другим словами, временное хранение предполагает, что к памяти имеется возможность доступа от какого-то устройства или от какой-то другой части схемы как с операцией записи, так и с операцией чтения (считывания). В зависимости от того, в каком порядке может записываться или читаться информация, существуют две разновидности ОЗУ:

- · ОЗУ с параллельным или произвольным доступом (это наиболее универсальная схема);

- · ОЗУ с последовательным доступом (это более специфическая схема).

Параллельный или произвольный доступ наиболее прост и обычно не требует никаких дополнительных элементов, так как именно на этот режим непосредственно рассчитаны микросхемы памяти. В этом режиме можно записывать информацию в любой адрес ОЗУ и читать информацию из любого адреса ОЗУ в произвольном порядке. Однако параллельный доступ требует формирования довольно сложных последовательностей всех входных сигналов памяти. То есть для записи информации необходимо сформировать код адреса записываемой ячейки и только потом подать данные, сопровождаемые управляющими сигналамиCS иWR (см. рис. 12.2). Точно так же необходимо подавать полный код адреса читаемой ячейки при операции чтения. Этот режим доступа чаще всего применяется в компьютерах и контроллерах, где самыми главными факторами являются универсальность и гибкость использования памяти для самых разных целей.

Последовательный доступ к памяти предполагает более простой порядок общения с памятью. В этом случае не надо задавать код адреса записываемой или читаемой ячейки, так как адрес памяти формируется схемой автоматически. Для записи информации надо всего лишь подать код записываемых данных и сопроводить его стробом записи. Для чтения информации надо подать строб чтения и получить читаемые данные. Автоматическое задание адреса при этом осуществляется внутренними счетчиками, меняющими свое состояние по каждому обращению к памяти. Например, десять последовательных циклов записи запишут информацию в десять последовательно расположенных ячеек памяти. Недостаток такого подхода очевиден: мы не имеем возможности записывать или читать ячейки с произвольными адресами в любом порядке. Зато существенно упрощается и ускоряется процедура обмена с памятью (запись и чтение). Мы будем в данном разделе рассматривать именно этот тип памяти, этот тип доступа.

Можно выделить три основных типа оперативной памяти с последовательным доступом:

- · память типа «первым вошел — первым вышел» (FIFO, First In — First Out);

- · память магазинного, стекового типа, работающая по принципу «последним вошел — первым вышел» (LIFO, Last In — First Out).

- · память для хранения массивов данных.

Два первых типа памяти подразумевают возможность чередования операций записи и чтения в памяти. При этом память FIFO выдает читаемые данные в том же порядке, в котором они были записаны, а память LIFO — в порядке, обратном тому, в котором они были записаны в память. Память FIFO можно сравнить со сдвиговым регистром, на выходе которого данные появляются в том же порядке, в котором они были в него записаны. А память LIFO обычно сравнивают с магазином для подачи патронов в автомате или пистолете, в котором первым выдается патрон, вставленный в магазин последним. Память с принципом LIFO используется, в частности, в компьютерах (стек), где она хранит информацию о параметрах программ и подпрограмм.

Для памяти FIFO требуется хранение двух кодов адреса (адрес для записи и адрес для чтения), для памяти LIFO достаточно одного кода адреса.

Хранение массивов в памяти предполагает, что сначала в память записывается целиком большой массив данных, а потом этот же массив целиком читается из памяти. Эта память также может быть устроена по двум принципам (FIFO и LIFO). В первом случае (FIFO) записанный массив читается в том же порядке, в котором и был записан, во втором случае (LIFO) — в противоположном порядке (начиная с конца). В обоих этих случаях для общения с памятью требуется хранить только один код адреса памяти.

Рассмотрим несколько примеров схем, реализующих перечисленные типы памяти с последовательным доступом.

Рис. 12.5. Функциональная схема памяти типа FIFO.

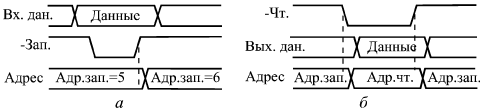

На рис. 12.5 представлена функциональная схема памяти типа FIFO на микросхемах с раздельными шинами входных и выходных данных. Адреса памяти задаются двумя счетчиками — счетчиком записи и счетчиком чтения, выходные коды которых мультиплексируются с помощью 2-канального мультиплексора. Запись данных осуществляется по стробу записи «-Зап.», чтение данных — по стробу чтения «-Чт.». Своим задним фронтом сигнал «-Зап.» переключает счетчик записи, а задний фронт сигнала «-Чт.» переключает счетчик чтения. В результате каждая следующая запись осуществляется в следующий по порядку адрес памяти. Точно так же каждое следующее чтение производится из следующего по порядку адреса памяти.

Перед началом работы необходимо сбросить счетчики в нуль сигналом «Сброс». При отсутствии операций записи и чтения память находится в состоянии чтения (сигналWR равен единице), а на адресные входы памяти подается код адреса записи со счетчика записи. При подаче строба записи «-Зап.» производится запись входных данных по адресу из счетчика записи. Входные (записываемые) данные должны выставляться раньше начала сигнала «-Зап.», а заканчиваться после этого сигнала. При подаче строба чтения «-Чт.» мультиплексор переключается на передачу адреса чтения, и на выходе памяти появляется информация, которая считывается из адреса чтения, задаваемого счетчиком чтения. Действительными выходные (читаемые) данные будут по заднему (положительному) фронту сигнала «-Чт.» .

Запись начинается с нулевого адреса памяти и производится по последовательно нарастающим адресам. Точно так же чтение начинается с нулевого адреса памяти и производится по последовательно нарастающим адресам. Операции записи и чтения могут чередоваться. Временные диаграммы циклов записи и чтения показаны на рис. 12.6.

Рис. 12.6. Временные диаграммы циклов записи (а)и чтения (б) для памяти типа FIFO.

В качестве счетчиков можно использовать нужное количество микросхем ИЕ 7, в качестве мультиплексора — микросхемы КП 11, в качестве памяти — К 155РУ 7 или любые другие нетактируемые микросхемы памяти с раздельными шинами входных и выходных данных.

Условия правильной работы схемы следующие. Длительность сигнала «-Зап.» не должна быть меньше минимально допустимой длительности сигналаWR памяти. Длительность сигнала «-Чт.» не должна быть меньше суммы задержки переключения мультиплексора и задержки выборки адреса памяти. Период следования сигнала «-Зап.» не должен быть меньше суммы задержки переключения счетчика записи и длительности сигнала «-Зап.». Период следования сигнала «-Чт.» не должен быть меньше суммы задержки переключения счетчика чтения и длительности сигнала «-Чт.» .

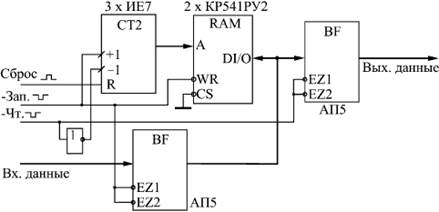

Функциональная схема памяти типа LIFO (рис. 12.7) проще по структуре, чем схема памяти FIFO, так как она содержит только один счетчик и не требует мультиплексирования. В данном случае считаем, что используется память с двунаправленной шиной входных/выходных данных.

Рис. 12.7. Функциональная схема памяти типа LIFO.

Счетчик адреса необходим реверсивный, с раздельными тактовыми входами прямого и обратного счета (например, ИЕ 7). После проведения цикла записи по заднему фронту сигнала «-Зап.» счетчик увеличивает свой выходной код (адрес памяти) на единицу. Перед проведением цикла чтения по переднему фронту сигнала «-Чт.» счетчик уменьшает свой выходной код на единицу. Такая организация перебора адресов позволяет организовать чтение из памяти в порядке, обратном порядку записи в память.

Например, пусть исходное состояние счетчика 2. Пусть мы производим три цикла записи: первый — в адрес 2, второй — в адрес 3, третий — в адрес 4. После третьего цикла записи счетчик будет выдавать код 5. Затем проведем три цикла чтения: первый — из адреса 4 (перед чтением адрес уменьшился на единицу), второй — из адреса 3, третий — из адреса 2. После третьего цикла чтения счетчик будет выдавать код 2. Мы вернулись в исходное состояние, прочитав записанную информацию в обратном порядке.

Исходное состояние счетчика в данной схеме вообще-то не слишком важно, так как не важен текущий адрес памяти, в который производится запись и из которого потом производится чтение. Однако в случае, когда используется начальный сброс счетчика в нулевое состояние (по сигналу «Сброс»), можно довольно просто организовать контроль за переполнением памяти LIFO из-за слишком большого количества записанной в нее информации. Для контроля переполнения можно использовать выходной сигнал переноса старшего счетчика (>15).

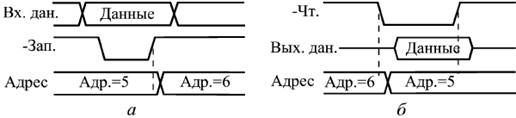

Временные диаграммы циклов записи и чтения приведены на рис. 12.8.

В цикле записи по сигналу «-Зап.» открывается входной буфер АП 5 и входные (записываемые) данные поступают на входы/выходы памяти. Одновременно по этому же сигналу память переходит в режим записи. В результате в текущий адрес памяти записываются входные данные, после чего адрес увеличивается на единицу. Входные данные должны начинаться до начала сигнала «-Зап.» и заканчиваться после его конца.

В цикле чтения по сигналу «-Чт.» адрес уменьшается на единицу, после чего открывается выходной буфер АП 5, который выдает на выход схемы читаемую из памяти информацию. Применение выходного буфера не обязательно, однако он предотвращает прохождение на шину выходных данных информации, записываемой в память в цикле записи. Выходные данные действительны по заднему фронту сигнала «-Чт.» .

Рис. 12.8. Временные диаграммы циклов записи (а) и чтения (б) для памяти типа LIFO.

Условия правильной работы схемы следующие. Длительность сигнала записи должна быть не меньше минимально допустимой длительности сигналаWR памяти. Период следования сигналов «-Зап.» не должен быть меньше суммы времени срабатывания счетчиков и длительности сигнала «-Зап.». Длительность сигнала чтения должна быть не меньше суммы времени срабатывания счетчика, времени выборки адреса памяти и задержки выходного буфера данных. Период следования сигналов «-Чт.» также не должен быть меньше этой же суммы. Память должна быть нетактируемой, например, КР 541РУ 2.

Наконец, третий тип памяти для временного хранения данных — память для хранения массивов данных. Рассмотрим вариант схемы такой памяти типа FIFO (рис. 12.9).

Адреса памяти в данном случае задаются одним единственным счетчиком, который работает в режиме только прямого счета. Перед началом работы необходимо сбросить счетчик (сигнал «Сброс»). Затем производится запись массива данных. При этом после каждого цикла записи по заднему фронту сигнала «-Зап.» выходной код счетчика увеличивается на единицу. После окончания записи всего массива снова надо сбросить счетчик в нуль (сигнал «Сброс»), а затем производить чтение массива, начиная с нулевого адреса. При этом после каждого цикла чтения по заднему фронту сигнала «-Чт.» выходной код счетчика опять же увеличивается на единицу. В результате массив данных читается в том же порядке, что и был записан. Контроль за длиной записываемого и читаемого массивов возлагается на внешнее по отношению к приведенной схеме устройство.

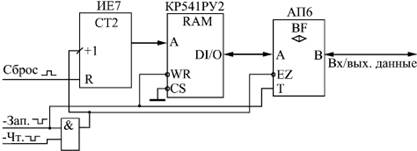

Рис. 12.9. Функциональная схема памяти для хранения массивов данных Для данной схемы должна использоваться нетактируемая память (например, КР 541РУ 2) с двунаправленной шиной входных/выходных данных. Считаем, что данные подаются на схему и читаются из схемы также по двунаправленной шине данных. Между памятью и этой шиной включается двунаправленный буфер (типа АП 6), который может понадобиться, например, для обеспечения большого выходного тока и малого входного тока со стороны внешней двунаправленной шины данных (это типичная ситуация при построении микропроцессорных и компьютерных систем). Буфер этот открывается на передачу данных в память по сигналу «-Зап.» (сигналEZ становится равным нулю, сигнал T также нулевой) и открывается для чтения данных из памяти по сигналу «-Чт.» (сигналEZ становится равным нулю, сигнал T равен единице).

Условия правильной работы схемы следующие. Длительность сигнала записи «-Зап.» должна быть не менее минимальной длительности сигналаWR памяти. Входные (записываемые) данные должны начинаться до начала сигнала «-Зап.», а заканчиваться после его окончания. Длительность сигнала чтения «-Чт.» не должна быть меньше суммы задержки буфера и времени выборки адреса памяти. Действительными читаемые данные будут по заднему фронту сигнала «-Чт.». За период следования сигналов «-Зап.» и «-Чт.» схема должна успевать выполнить операцию записи и чтения соответственно, кроме того, должен успеть полностью переключиться счетчик адреса памяти.