Разработка принципиальной схемы буфера TLB

Однако, вполне возможно, что все строки на данной горизонтали окажутся достоверными. Тогда информацию из какой-то строки придется удалить, а на ее место загрузить новый начальный адрес. МП при этом стремиться удалить начальный адрес той страницы, к которой он обращался наиболее давно. В этом ему «помогают» биты LRU (last recently used — «наиболее давно использовал») b0 -b2. Обозначим строки… Читать ещё >

Разработка принципиальной схемы буфера TLB (реферат, курсовая, диплом, контрольная)

Страничный механизм (рассмотренный в п. 3.3) требует значительных временных затрат. Поэтому в МП вводится дополнительная внутренняя кэш-память страниц, в которой хранятся начальные адреса (вернее 20-ть старших разрядов адреса, поскольку 12-ть младших разрядов начального адреса страницы равны 0) страниц, с которыми МП работал в последнюю очередь. Процент кэш-попаданий в буфер TLB составляет порядка 95 — 98%. И только при кэш-промахе включается страничный механизм.

Кэш-память страниц состоит из трех блоков: блок данных, блок тэгов и блок LRU/достоверности (см. рис. 4.1). Блок данных разбивается на строки. Всего этих строк 4Ч8 = 32. Каждая строка имеет формат 20 бит. В строке содержится начальный адрес страницы (вернее 20 старших разрядов этого адреса). Каждой строке ставится в соответствие свой тэг в блоке тэгов. Тэг имеет формат 17 бит.

Всю кэш-память страниц можно условно разбить на 8-мь горизонталей. На каждой горизонтали располагаются четыре строки, соответствующие этим строкам четыре тэга и один 7-ми битовый элемент LRU/достоверности.

Рис. 4.1. Графическое представление функционирования буфера TLB

Рассмотрим работу кэш-памяти страниц [7]:

1. Вариант, когда МП ищет в буфере начальный адрес нужной ему страницы и там его не находит (кэш-промах).

МП выработал линейный адрес (Ал). Поскольку включен страничный механизм, этот адрес еще не является физическим (Аф). Пусть при поиске (соответствующего этому Ал) начального адреса страницы в буфере TLB произошел кэш-промах. При этом начинает работать рассмотренный ранее громоздкий страничный механизм. Когда МП в соответствующей таблице страниц найдет нужный элемент PTE, он извлечет из этого элемента 20-ть старших разрядов начального адреса страницы, пристыкует к ним 12-ти разрядное смещение OFFSET (из Ал) и сформирует тем самым искомый Аф. Одновременно МП возьмет найденные им в PTE 20-ть старших разрядов начального адреса страницы и загрузит их в одну из строк блока данных буфера TLB. При этом важным является то, что данный начальный адрес не может попасть в любую произвольную строку блока данных, он может попасть только в одну из четырех строк на конкретной горизонтали! Номер горизонтали определяют при этом разряды 14 — 12 линейного адреса Ал.

Когда МП при кэш-промахе загружает в какую-либо строку буфера новый начальный адрес страницы он одновременно копирует в соответствующий этой строке тэг 17-ть старших разрядов Ал (разряды 31 — 15). Открытым пока остается вопрос, а в какую из четырех строк на известной горизонтали попадет (при кэш-промахе) наш начальный адрес. Определение номера строки на известной горизонтали, в которую попадет начальный адрес страницы, осуществляется на основании информации, записанной в элементе LRU/достоверности данной горизонтали.

Вернемся к началу процесса. МП выработал Ал. МП берет разряды 14 -12 этого адреса и определяет горизонталь в буфере TLB. Затем МП берет старшие 17-ть разрядов Ал и сравнивает их со всеми четырьмя тэгами, расположенными на выбранной горизонтали. При этом возможны два варианта: произошло сравнение с одним из тэгов или сравнений не произошло совсем. Несколько сравнений сразу произойти здесь не может, так как алгоритм заполнения кэш-памяти таков, что на одной горизонтали не может оказаться одинаковых тэгов.

Если сравнений не произошло, значит произошел кэш-промах.

2. Вариант, когда МП ищет в буфере начальный адрес нужной ему страницы и там его находит (кэш-попадание).

Если сравнение с одним из тэгов произошло — это кэш-попадание. МП достает из соответствующей этому тэгу строки 20-ть старших разрядов начального адреса страницы, пристыковывает к ним 12-ть младших разрядов Ал (OFFSET) и тем самым формирует искомый Аф.

Любой элемент LRU/достоверности имеет формат, приведенный на рис. 4.2.

b0. | b1. | b2. | a0. | a1. | a2. | a3. |

Рис. 4.2. Формат элемента LRU/Достоверности

Где a0 — a3 -биты достоверности. Каждый бит достоверности соответствует одной из четырех расположенных на данной горизонтали строк. Когда МП после кэш-промаха загружает «на горизонталь» новый начальный адрес страницы, он, прежде всего, последовательно проверяет биты достоверности, расположенные на данной горизонтали. Если при этом МП встречает строку, объявленную недостоверной, именно в нее и будет загружен новый адрес.

Однако, вполне возможно, что все строки на данной горизонтали окажутся достоверными. Тогда информацию из какой-то строки придется удалить, а на ее место загрузить новый начальный адрес. МП при этом стремиться удалить начальный адрес той страницы, к которой он обращался наиболее давно. В этом ему «помогают» биты LRU (last recently used — «наиболее давно использовал») b0 -b2. Обозначим строки на горизонтали L0, L1, L2 и L3. При кэш-попаданиях МП всегда формирует заново биты LRU по схеме, приведенной на рис. 4.3.

Рис. 4.3. Алгоритм формирования битов LRU

Отсюда вытекает алгоритм удаления строк, приведенный в таблице 4.1.

Таблица 4.1. Алгоритм удаления строк в буфере TLB

b0. | b1. | b2. | Строка для удаления. |

Безразлично. | L0. | ||

Безразлично. | L1. | ||

безразлично. | L2. | ||

безразлично. | L3. |

По рассмотренному выше механизму работы буфера TLB была разработана функциональная схема адресного КЭШ, представленная на рис. 4.4.

Для более наглядного представления функциональной схемы будем считать, что все элементы, необходимые для ее выполнения, существуют и имеют необходимую организацию, разрядность и т. д. Т.к. наращивание до необходимой разрядности не представляет сложности, но существенно влияет на размер, занимаемый схемой, и на количество неиспользованных входов и выходов.

Рассмотрим функционирование разработанной схемы.

После того как МП сформировал линейный адрес (Ал) и выставил его на шину, он формирует сигналы управления буфером TLB: CR/W# и bitR#. Сигнал CR/W# задает режим чтения (при H — уровне)/записи (при L — уровне) в КЭШ; сигнал bitR# = L — задает режим сброса бита достоверности для текущего адреса на шине (если такой имеется в КЭШ). Выполняемые действия буфера TLB при конкретных значениях сигналов приведены таблице 4.2.

При чтении буфер TLB принимает с AB старшие 20-ть бит линейного адреса. Младшие 3 из принятых бит являются индексом, а старшие 17 — тэгом. Индекс используется в качестве адреса при обращении к блокам: тэгов, данных и битов LRU/достоверности. Режим чтения активирует выбор кристалла всех 4-х микросхем памяти блока тэгов (SRAM1-SRAM4), после чего происходит сравнение 4-х выбранных из памяти тэнов с тэгом с AB.

Таблица 4.2. Функционирование адресного КЭШ

CR/W#. | bitR#. | Режим функционирования буфера TLB. |

Запись в КЭШ. | ||

Сброс бита достоверности для текущего адреса (если он имеется в КЭШ). | ||

Чтение из КЭШ. |

Если сравнение произошло и данная строка является достоверной, то происходит выбор конкретной микросхемы памяти в блоке данных. После чего считанные данные выдаются на шину AB и вырабатывается сигнал СasheHit=1, означающий попадание в КЭШ. Также происходит формирование новых значений битов LRU (Блок формирования битов LRU/достоверности) и их запись в блок LRU/достворености. Если CasheHit=0 (кэш-промах), МП должен включить страничное преобразование, после чего сформированный адрес должен быть записан в буфер TLB.

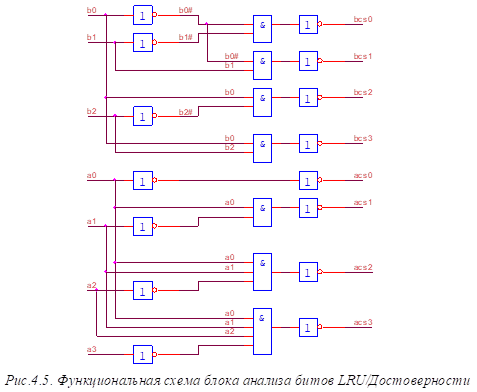

При записи в КЭШ происходит анализ битов достоверности/LRU (Блок анализа битов LRU/Достоверности и MUX1) для выбранной горизонтали, необходимый для формирования сигналов выбора конкретных микросхем памяти в блоке тэгов и данных. Биты достоверности и LRU анализируются раздельно. Если на выбранной горизонтали есть недостоверные строки, то выбирается первая из них, если же все строки достоверны, то выбор строки для удаления производится с использованием битов LRU по вышеописанному алгоритму (табл.4.1.). Удаление выбранной строки происходит за счет записи на ее место новой информации (во всех блоках буфера TLB).

Режим сброса бита достоверности отличается от режима чтения лишь тем, что при кэш-попадании в этом режиме информация на шину AB не выдается и сбрасывается бит достоверности для заданного адреса.

Функциональная схема и таблица функционирования блоков анализа битов LRU/достоверности и блока их обновления представлены на рис. 4.5. и в табл.4.3. и на рис. 4.6. и в табл.4.4. соответственно.

Таблица 4.3. Функционирование блока анализа битов LRU/Достоверности.

Анализ битов достоверности. | ||||||||

Значения битов. | Значения сигналов выбора микросхем памяти. | Выбираемая строка на горизонтали. | ||||||

a0. | a1. | a2. | a3. | acs0. | acs1. | acs2. | acs3. | |