Разработка блока преобразования виртуальных адресов

Структура ОП, а также формат виртуального адреса рассмотрены в разделе — оперативная память, поэтому перейдём к описанию общей последовательности действий при преобразовании виртуального адреса: Два управляющих бита: бит достоверности (показывает изменились ли данные в ОП с момента внесения адреса в кэш) и резервный бит, которые может использоваться операционной системой. Из базового регистра… Читать ещё >

Разработка блока преобразования виртуальных адресов (реферат, курсовая, диплом, контрольная)

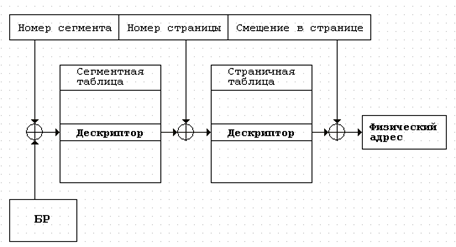

Структура ОП, а также формат виртуального адреса рассмотрены в разделе — оперативная память, поэтому перейдём к описанию общей последовательности действий при преобразовании виртуального адреса:

- 1. Из базового регистра (в данной реализации используется внутренний регистр процессора) извлекается физический адрес начала таблицы сегментов и суммируется с номером сегмента.

- 2. По полученному физическому адреса из ОП извлекается дескриптор сегмента, хранящий в себе физический адрес начала своей страничной таблицы, а также два бита, которые могут быть использованы операционной системой, например, для управления защитой от несанкционированного доступа.

- 3. Физический адрес начала страничной таблицы сегмента суммируется с номером страницы.

- 4. По полученному физическому адресу из ОП извлекается дескриптор страницы, содержащий физический адрес страницы в ОП, бит присутствия и бит модификации.

- 5. Анализируется значение бита присутствия:

- · 1 — страница находится в ОП;

- · 0 — страница выгружена из ОП.

В случае, когда страницы нет в ОП и микрокомандой разрешены страничные прерывания, в контроллер прерываний подаётся запрос на страничное прерывание.

В результате выполнение активной задачи прерывается, управление передаётся операционной системе. Операционная система копирует запрошенную страницу с диска в ОП и возвращает управление прерванной задаче. При отсутствии свободного места в ОП, нужно удалить одну из страниц, уже имеющихся в ОП. Выбор удаляемой страницы возлагается на алгоритм замещения страниц. Наиболее популярным алгоритмом является алгоритм удаления наиболее давно использовавшихся страниц (Least Recently Used, LRU), но в данной реализации ОП в дескрипторе страницы не выделяется место под биты, необходимые для алгоритма LRU. В связи с этим, операционной системой может быть использован алгоритм случайного выбора заменяемой страницы. Так как количество страниц в памяти велико, то вероятность удачного выбора высока и этот алгоритм даёт хорошую эффективность. Бит модификации указывает на то, была ли страница изменена во время хранения в ОП. Модифицированная страница перед удалением из ОП должна быть записана на диск.

6. Полученный физический адрес начала страницы суммируется с 12-разрядным смещением в странице, образуя физический адрес требуемой ячейки памяти.

Схема преобразования виртуального адреса в физический представлена на рис. 21.

Рис. 21 Схема преобразования виртуального адреса в физический.

В процедуре преобразования адреса, а также в алгоритмах замещения виртуальных страниц и работе с КЭШем большая роль отводится микропрограммному управлению и использованию вычислительной мощности ЦП. Можно даже сказать, что разработанная схема предоставляет процессору интерфейс для реализации алгоритмов свопинга, алгоритмов защиты данных и работы с КЭШем.

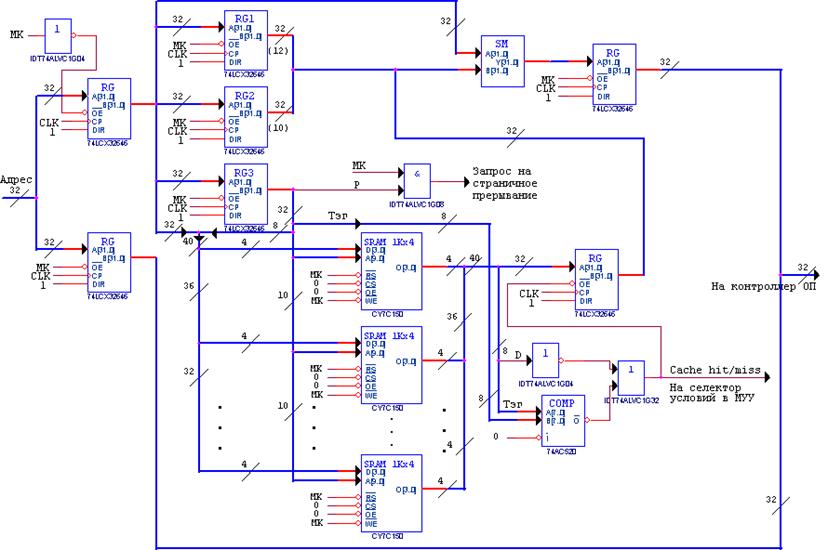

Рассмотрим особенности реализации блока:

- 1. Установкой соответствующего биты микрокоманды осуществляется разрешение и блокировка работы блока преобразования адресов. При отключении блока процессор может обращаться к ОП по физическому адресу, что необходимо для первоначальной инициализации системы, построения таблиц векторов прерываний, сегментных и соответствующих им страничных таблиц, а также для адресации внешних запоминающих устройств, таких как: «винчестер», НГМД, оперативная память видеоадаптера.

- 2. Преобразование адресов, замещение виртуальных, чтение и запись в кэш требуют значительного числа циклов процессора. Для этого в блок включено три регистра для хранения промежуточных значений: RG1, RG2 и RG3, которые могут быть использованы операционной системой на своё усмотрение. Но при проектировании им отводились следующие роли:

- · RG1 — хранение смещение в странице (младшие 12 разрядов адреса);

- · RG2 — хранение номер страницы (10 разрядов адреса);

- · RG3 — хранение первоначального значения виртуального адреса.

- 3. Кэш строится на 10-ти микросхемах SRAM информационной организацией 1Kx4, что позволяет хранить 1K слов разрядностью 40. В каждой слово входят:

- · тэг, в качестве которого используется номер сегмента, так как смена сегмента происходит относительно редко, поэтому можно рассчитывать на высокую эффективность КЭШа — 8 разрядов;

- · физический адрес начала страницы, это также сделано для повышения эффективности использования КЭШа и уменьшения числа его перезаписей, для получения физического адреса ячейки остаётся только прибавить смещение в 8 младших разрядов — 30 разрядов;

- · два управляющих бита: бит достоверности (показывает изменились ли данные в ОП с момента внесения адреса в кэш) и резервный бит, которые может использоваться операционной системой.

Адресация КЭШа происходит номером страницы (10 разрядов). После чтения слова из КЭШа происходит сравнение полученного тэга с искомым (8 разрядов) и далее анализ бита достоверности. Результат анализа передаётся на селектор выбора условий в МУУ в качестве бита Cache hit / miss (попадание / промах — 0 / 1) для использования микропрограммой.

4. Для управления КЭШем имеются сигналы WE# (разрешение записи) и RS# (стирание).

Схема подключения буфера TLB и блока преобразования виртуальных адресов представлена на структурной схеме процессора (рис. 7).

На схеме блока используются следующие обозначения:

- · MK — бит микрокоманды;

- · P — бит присутствия;

- · D — бит достоверности;

- · Cache hit / miss — бит попадания / промаха КЭШа;

- · Тэг — номер сегмента;

- · CLK — системный синхросигнал.

Принципиальная схема блока преобразования виртуальных адресов представлена на рис. 22.

На схеме используются следующие номиналы микросхем:

- · 74LCX32646 — 32-разрядный регистр;

- · CY7C150 — SRAM 1Kx4;

- · 74AC520 — 8-разрядный компаратор;

- · IDT74ALVC1G08 — логический элемент И;

- · IDT74ALVC1G32 — логический элемент ИЛИ;

- · IDT74ALVC1G04 — инвертор.

Рис. 22 Принципиальная схема блока преобразования виртуальных адресов