Исследование работы АЛУ и кэш-памяти

Ввести в модель учебной ЭВМ текс программы, ассемблировать его и сохранить на диске в виде txt-файла. При 8 ячейках памяти режим записиобратная, алгоритм замещенияс учетом бита записи, очередь. При 8 ячейках памяти режим записиобратная, алгоритм замещенияс учетом бита записи, очередь. В шаговом режиме выполнить программу, фиксируя после каждого шага состояние кэш-памяти. Установить размер… Читать ещё >

Исследование работы АЛУ и кэш-памяти (реферат, курсовая, диплом, контрольная)

Лабораторная работа № 7.

Тема: «Исследование работы АЛУ и кэш-памяти».

Цель работы: Исследовать работу АЛУ и кэш-памяти.

Оборудование: Персональный компьютер.

Программное обеспечение: Electronics Workbench, учебная ЭВМ.

Наглядные пособия: Руководство по выполнению задания, лекционный материал.

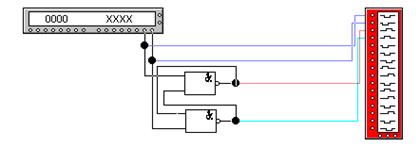

Порядок выполнения С помощью учебной ЭВМ исследовать работу кэш памяти (учебная ЭВМ находиться на program$, в папке Задание 2).

Исследовать работу полусумматора (см. Задание № 2).

Исследовать работу одноразрядного двоичного сумматора (см. Задание № 3).

Исследовать работу сумматора (см. Задание № 4).

Исследовать работу мультиплексора (см. Задание № 5).

Исследовать работу демультиплексора (см. Задание № 6).

Исследовать работу дешифратора (см. Задание № 7).

Исследовать работу шифратора (см. Задание № 8).

Исследовать работу асинхронного RS-триггера на элементах И-НЕ (см. Задание № 9).

Исследовать работу синхронного RS-триггера на элементах И-НЕ (см. Задание № 10).

Исследовать работу двухтактного RS-триггера на элементах И-НЕ (см. Задание № 11).

Исследовать JK — триггер (см. Задание № 12).

Часть 1. «Изучение принципов работы кэш-памяти».

Задание:

Набрать программу 1 .

Записать изменения кэш-памяти в отчет.

Изменить количество ячеек памяти с 4 до 8.

Записать программу 2.

Записать изменения ячеек кэш памяти при выполнении программы 2.

Изменить количество ячеек памяти с 4 до 8.

Программа 1.

WR #12.

WR 10.

WR @10.

ADD 12.

WR R0.

SUB 10.

PUSH R0.

При 4 ячейках памяти установить параметры КЭШа: режим записисквозная, алгоритм замещениябез учета бита записи, случайное замещение.

При 8 ячейках памяти режим записиобратная, алгоритм замещенияс учетом бита записи, очередь.

Программа 2.

RD #11.

WR R2.

WR -@R2.

PUSH R2.

CALL 005.

POP R3.

RET.

При 4 ячейках памяти установить параметры КЭШа: режим записисквозная, алгоритм замещениябез учета бита записи, бит использования.

При 8 ячейках памяти режим записиобратная, алгоритм замещенияс учетом бита записи, очередь .

ПОРЯДОК РАБОТЫ: Для программы 1 и2.

Ввести в модель учебной ЭВМ текс программы, ассемблировать его и сохранить на диске в виде txt-файла.

Установить параметры кэш-памяти размером 4 ячейки, выбрать режим записи и алгоритм замещения в соответствии с первой строкой своего варианта.

В шаговом режиме выполнить программу, фиксируя после каждого шага состояние кэш-памяти.

Установить размер кэш-памяти на 8 ячеек и выполнить программу в шаговом режиме еще раз.

Часть 2. «Исследование сумматоров».

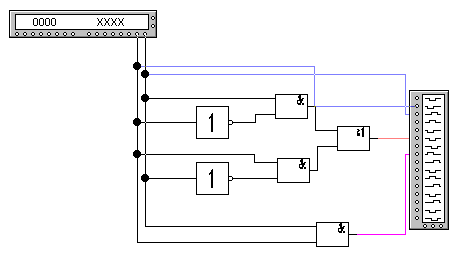

Задание № 2 Исследуйте работу полусумматора:

Рис. 1 — Схема полусумматора

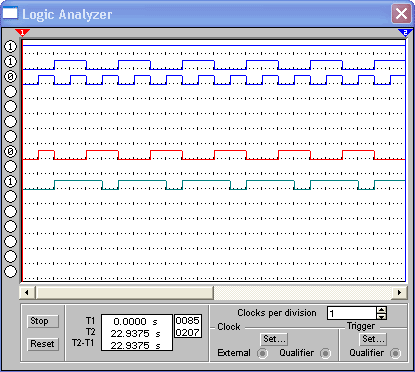

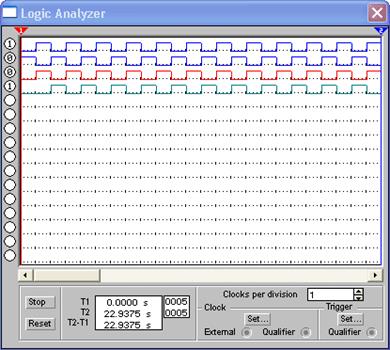

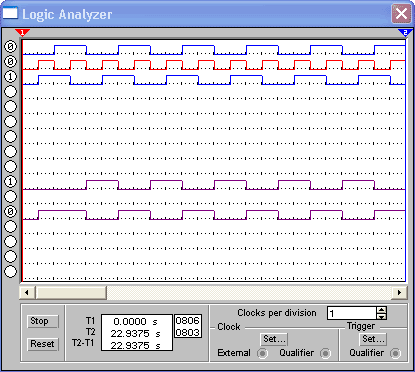

Рис. 2 — Диаграмма работы полусумматора

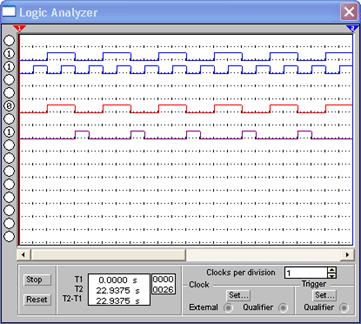

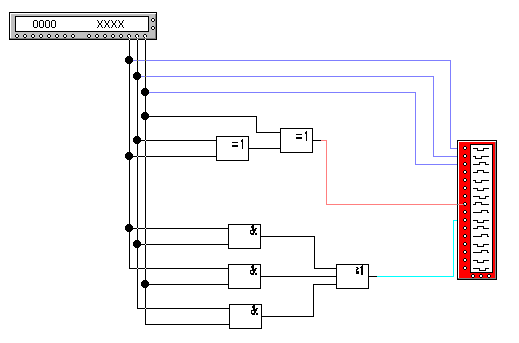

Задание № 3.

Исследуйте работу одноразрядного двоичного сумматора:

Рис. 3 — Схема одноразрядного двоичного сумматора

Рис. 4 — Диаграмма работы одноразрядного двоичного сумматора

память шифратор мультиплексор триггер Часть 3. «Исследование мультиплексоров и демультиплексоров».

Задание № 4 Исследуйте работу мультиплексора, в соответствии с вариантом:

В-1. | В-2. | В-3. | В-4. | В-5. |

74150N. | 74151N. | 74153N. | 74251J. | 74251N. |

Задание № 5 Исследуйте работу демультиплексора, в соответствии с вариантом:

В-1. | В-2. |

74155N. | 74156N. |

Часть 4. «Исследование дешифраторов и шифраторов».

Задание № 6 Исследуйте работу дешифратора, в соответствии с вариантом:

В-1. | В-2. | В-3. |

74145N. | 7442N. | 74LS42D. |

Задание № 7 Исследуйте работу шифратора типа 74147N.

Часть 5: «Исследование триггеров».

Краткие теоретические сведения Триггер — цифровой автомат, имеющий два устойчивых состояния равновесия либо 0, либо 1.

Типы триггеров:

Триггер типа RS имеет два входа раздельной установки в нулевое и единичное состояния. Воздействие по входу S (обозначен по первой букве слова set — установка) приводит триггер в единичное состояние, а воздействие по входу R (от первой буквы слова reset — сброс) — в нулевое. Одновременная подача сигналов S и R не допускается, что является недостатком для RS-триггера.

Триггер типа D (от слова delay — задержка) принимает информацию по одному входу и реализует функцию временной задержки. D-триггер имеет только режимы установки 1 и 0. В связи с этим несинхронизируемый D-триггер не применяется, т.к. его выход будет просто повторять входной сигнал.

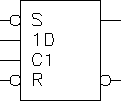

Рис. 5 — Условное обозначение D-триггера

Параметры синхронного Dтриггера:

D — информационный вход триггера C — синхронизирующий вход S — установка 1 R — установка 0 Q — информационный выход Q^ - инверсный информационный выход Параметры S и R служат для задания начальных условий.

Триггер типа JK — универсален, с раздельной установкой нулевого и единичного состояния, в зависимости от соединения его входов он может работать как RS, T, D триггера. В отличие от триггера типа RS в нем не запрещена одновременная подача сигналов на оба входа. Входы J и K эквивалентны входам S и R установки триггера соответственно в состояния «1» и «0».При объединении входов J и K и при подаче на них счетных импульсов. Вход J при раздельном использовании входов играет роль входа установки в единицу, а вход K — роль входа установки в нуль.

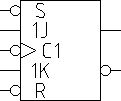

Рис. 6 — Условное обозначение JK-триггера

Параметры синхронного JK-триггера:

C — синхронизирующий вход J и K — информационные входы триггера S — установка 1 R — установка 0 Q — информационный выход Q^ - инверсный информационный выход Параметры S и R служат для задания начальных условий.

Триггер типа T называется триггером со счетным входом (или счетным триггером). Он изменяет свое состояние на противоположное каждый раз, когда на его вход приходит очередной сигнал. Обозначение триггера пришло от первой буквы анг. слова toggle-защелка.

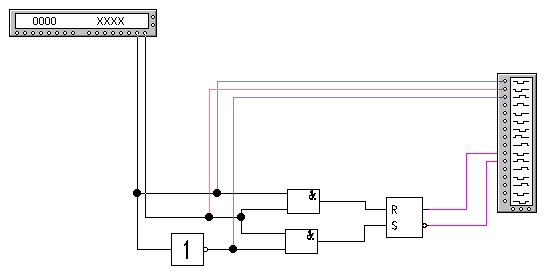

Задание № 9 Исследуйте работу асинхронного RS-триггера на элементах И-НЕ (Рис. 7):

Рис. 7 — Схема асинхронного RS-триггера на элементах И-НЕ

Рис. 8 — Диаграмма работы асинхронного RS-триггера

Задание № 10 Исследуйте работу синхронного RS-триггера на элементах И-НЕ (Рис. 9):

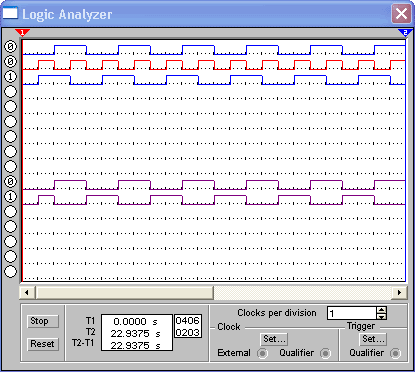

Рис. 9 — Схема синхронного RS-триггера

Рис. 10 — Диаграмма работы синхронного RS-триггера

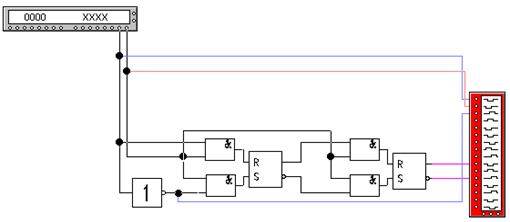

Задание № 11 Исследуйте работу двухтактного RS-триггера на элементах И-НЕ (Рис. 11):

Рис. 11 — Схема двухтактного RS-триггера

Рис. 12 — Диаграмма работы двухтактного RS-триггера

Задание № 12 Исследуйте на выбор любой JK — триггер.