Функциональная схема МК ATmega128

Регистр статуса содержит информацию о результате только что выполненной арифметической инструкции. Данная информация может использоваться для ветвления программы по условию. Следует понимать, что регистр статуса обновляется после выполнения всех операций АЛУ в объеме, предусмотренном для каждой конкретной инструкции. Флаги этого регистра в большинстве случаев позволяют отказаться от использования… Читать ещё >

Функциональная схема МК ATmega128 (реферат, курсовая, диплом, контрольная)

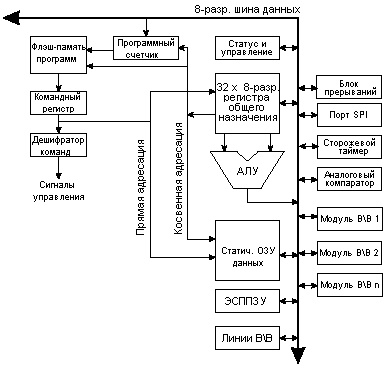

ATmega128 содержит следующие элементы: 128 кбайт внутрисистемно программируемой флэш-памяти с поддержкой чтения во время записи, 4 кбайт ЭСППЗУ, 4 кбайт статического ОЗУ, 53 линии универсального ввода-вывода, 32 универсальных рабочих регистра, счетчик реального времени (RTC), четыре гибких таймера-счетчика с режимами сравнения и ШИМ, 2 УСАПП, двухпроводной последовательный интерфейс ориентированный на передачу байт, 8-канальный 10-разр. АЦП с опциональным дифференциальным входом с программируемым коэффициентом усиления, программируемый сторожевой таймер с внутренним генератором, последовательный порт SPI, испытательный интерфейс JTAG совместимый со стандартом IEEE 1149.1, который также используется для доступа к встроенной системе отладке и для программирования, а также шесть программно выбираемых режимов уменьшения мощности.

Режим холостого хода (Idle) останавливает ЦПУ, но при этом поддерживая работу статического ОЗУ, таймеров-счетчиков, SPI-порта и системы прерываний. Режим выключения (Powerdown) позволяет сохранить содержимое регистров, при остановленном генераторе и выключении встроенных функций до следующего прерывания или аппаратного сброса. В экономичном режиме (Power-save) асинхронный таймер продолжает работу, позволяя пользователю сохранить функцию счета времени в то время, когда остальная часть контроллера находится в состоянии сна. Режим снижения шумов АЦП (ADC Noise Reduction) останавливает ЦПУ и все модули ввода-вывода, кроме асинхронного таймера и АЦП для минимизации импульсных шумов в процессе преобразования АЦП. В дежурном режиме (Standby) кварцевый/резонаторный генератор продолжают работу, а остальная часть микроконтроллера находится в режиме сна. Данный режим характеризуется малой потребляемой мощностью, но при этом позволяет достичь самого быстрого возврата в рабочий режим. В расширенном дежурном режиме (Extended Standby) основной генератор и асинхронный таймер продолжают работать.

Основная часть микроконтроллера ATmega128 — ядро центрального процессорного устройства AVR. Основная функция ядра ЦПУ заключается в гарантии корректности выполнения программы. Помимо этого, ЦПУ должен иметь возможность адресоваться к различным видам памяти, выполнять вычисления, управлять периферийными устройствами и обрабатывать прерывания.

Рисунок 13 — Функциональная схема архитектуры AVR.

В целях достижения максимальной производительности и параллелелизма у AVR-микроконтроллеров используется Гарвардская архитектура с раздельными памятью и шинами программ и данных.

Команды в памяти программ выполняются с одноуровневой конвейеризацией. В процессе выполнения одной инструкции следующая предварительно считывается из памяти программ. Данная концепция позволяет выполнять одну инструкцию за один машинный цикл. Память программ представляет собой внутрисистемно программируемую флэш-память.

Регистровый файл с быстрым доступом содержит 32 8-разрядных рабочих регистров общего назначения с однотактовым циклом доступа. Благодаря этому достигнута однотактность работы арифметико-логического устройства (АЛУ). При обычной работе АЛУ сначала из регистрового файла загружается два операнда, затем выполняется операция, а после результат отправляется обратно в регистровый файл и все это происходит за один машинный цикл.

6 регистров из 32 могут использоваться как три 16-разр. регистра косвенного адреса для эффективной адресации в пределах памяти данных. Один из этих указателей адреса может также использоваться как указатель адреса для доступа к таблице преобразования во флэш-памяти программ. Данные 16-разр. регистры называются X-регистр, Y-регистр и Z-регистр и описываются далее в этом разделе.

АЛУ поддерживает арифметические и логические операции между регистрами, а также между константой и регистром. Кроме того, АЛУ поддерживает действия с одним регистром. После выполнения арифметической операции регистр статуса обновляется для отображения результата выполнения операции.

Для ветвления программы поддерживаются инструкции условных и безусловных переходов и вызовов процедур, позволяющих непосредственно адресоваться в пределах адресного пространства. Большинство инструкций представляют собой одно 16-разр. слово. Каждый адрес памяти программ содержит 16- или 32-разр. инструкцию. Флэш-память программ разделена на две секции: секция программы начальной загрузки и секция прикладной программы. Обе секции имеют раздельные биты защиты от записи и чтения/записи. Инструкция SPM (запись в секцию прикладной программы) должна использоваться только внутри секции программы начальной загрузки.

При генерации прерывания и вызове подпрограмм адрес возврата из программного счетчика записывается в стек. Стек эффективно распределен в статическом ОЗУ памяти данных и, следовательно, размер стека ограничен общим размером статического ОЗУ и используемым его объемом. В любой программе сразу после сброса должна быть выполнена инициализация указателя стека (SP) (т.е. перед выполнением процедур обработки прерываний или вызовом подпрограмм). Указатель стека — SP — доступен на чтение и запись в пространстве ввода-вывода. Доступ к статическому ОЗУ данных может быть легко осуществлен через 5 различных режимов адресации архитектуры AVR.

Гибкий модуль прерываний содержит свои управляющие регистры в пространстве ввода-вывода и имеет дополнительный бит общего разрешения работы системы прерываний в регистре статуса. У всех прерываний имеется свой вектор прерывания в соответствии с таблицей векторов прерываний. Прерывания имеют приоритет в соответствии с позицией их вектора. Прерывания с меньшим адресом прерывания имеют более высокий приоритет.

Пространство памяти ввода-вывода содержит 64 адреса с непосредственной адресацией или может адресоваться как память данных, следующая за регистрами по адресам $ 20 — $5 °F. Кроме того, ATmega128 имеет пространство расширенного ввода-вывода по адресам $ 60 — $FF в статическом ОЗУ, для доступа к которому могут использоваться только процедуры ST/STS/STD и LD/LDS/LDD.

АЛУ AVR-микроконтроллеров работает в непосредственной связи со всеми 32 универсальными рабочими регистрами. АЛУ позволяет выполнить за один машинный цикл операцию между двумя регистрами или между регистром и константой. Операции АЛУ могут быть классифицированы на три группы: арифметические, логические и битовые. Кроме того, архитектурой ATmega128 поддерживаются операции умножения со знаком и без знака и дробным форматом.

Регистр статуса содержит информацию о результате только что выполненной арифметической инструкции. Данная информация может использоваться для ветвления программы по условию. Следует понимать, что регистр статуса обновляется после выполнения всех операций АЛУ в объеме, предусмотренном для каждой конкретной инструкции. Флаги этого регистра в большинстве случаев позволяют отказаться от использования инструкций сравнения, делая код программы более компактным и быстрым.

Состояние регистра статуса автоматически не запоминается при вызове процедуры обработки прерываний и не восстанавливается при выходе из нее. Это необходимо выполнять программно.

Регистр статуса SREG AVR-микроконтроллера имеет следующую структуру:

Разряд 7 — I: Общее разрешение прерываний Бит общего разрешения прерываний используется для активизации работы системы прерываний. Разрешение отдельных прерываний осуществляется в соответствующих управляющих регистрах. Если бит общего разрешения прерываний сбросить, то ни одно из прерываний не будет активным независимо от их индивидуальной конфигурации. Бит I сбрасывается в 0 аппаратно после генерации запроса на прерывание, а после выполнения инструкции возврата из прерывания RETI снова устанавливается к 1 для выполнения последующих прерываний. Бит I может также сбрасываться и устанавливаться с помощью инструкций CLI и SEI, соответственно.

Разряд 6 — T: Хранение копируемого бита Специальные битовые операции BLD (копирование из Т-бита) и BST (копирование в Т-бит) используют в качестве источника и получателя данных бит T. Любой бит из регистрового файла может быть скопирован в бит T инструкцией BST, а также содержимое бита Т может быть скопировано в любой бит регистрового файла с помощью инструкции BLD.

Разряд 5 — H: Флаг половинного переноса Данный флаг устанавливается при выполнении некоторых арифметических инструкций и индицирует о возникновении половинного переноса. Как правило половинный перенос широко используется в двоично-десятичной арифметике.

Разряд 4 — S: бит знака, S = Искл. ИЛИ (N,?V).

Бит S — результат выполнения логической операции исключающего ИЛИ между флагом отрицательного результата N и флагом переполнения двоичного дополнения V.

Разряд 3 — V: Флаг переполнения двоичного дополнения Флаг переполнения двоичного дополнения V поддерживает арифметику с двоичным дополнением.

Разряд 2 — N: Флаг отрицательного результата Флаг отрицательного результата N индицирует, что результатом выполнения арифметической или логической операции является отрицательное значение.

Разряд 1 — Z: Флаг нулевого результата Флаг нулевого результата Z индицирует, что результатом выполнения арифметической или логической операции является ноль.

Разряд 0 — C: Флаг переноса.