Инструментальные средства измерительного модуля системы

Входной сигнал БВВ может быть протрассирован через входной триггер или непосредственно к блокам внутренней логики. Каждый входной буфер может быть сконфигурирован таким образом, чтобы удовлетворять одному из стандартов ввода-вывода, поддерживаемых устройством. Выводной сигнал проходит через буфер с тремя состояниями, который подсоединен непосредственно к выводу микросхемы. Сигнал может быть… Читать ещё >

Инструментальные средства измерительного модуля системы (реферат, курсовая, диплом, контрольная)

1 ПЛИС семейства Spatran-II фирмы Xilinx.

Семейство Spatran-II [10] - второе поколение ПЛИС, предназначенных для использования в крупно серийных проектах. Данные ПЛИС применяются в проектах как альтернатива специализированным не перепрограммируемым интегральным схемам емкостью до 200 тысяч вентилей и системным быстродействием до 200 МГц, частотах внутри кристалла, превышающих 350МГц, с напряжением питания ядра кристалла 2,5 В.

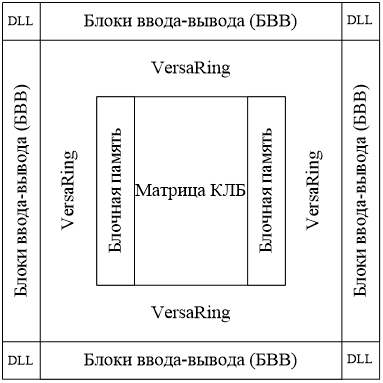

Каждый кристалл данного семейства состоит из матрицы конфигурируемых логических блоков (КЛБ), которая окружена программируемыми блоками ввода-вывода (БВВ), соединение которых осуществляется с помощью набора иерархических высокоскоростных программируемых трассировочных ресурсов.

Рис. 4. Структура архитектуры Spartan-II

ПЛИС производится на основе статического операционного запоминающего устройства, поэтому функционирование кристаллов определяется загруженными во внутренние ячейки памяти конфигурационными данными, которые загружаются из внешнего постоянного запоминающего устройства и загружаются в ПЛИС сразу после включения питания автоматически или принудительно, количество загрузок при этом является неограниченным. Конфигурационные данные создаются пользователем при помощи ПО проектирования Xilinx Foundation или Alliance Series.

Из рис. 4 видно, что основными элементами являются матрица КЛБ, блочная память, локальные трассировочные ресурсы VersaBlock, ББВ и четыре модуля автоподстройки задержек (DLL).

На основе КЛБ реализуется вся логика. Базовым элементом блока является логическая ячейка (ЛЯ), состоящая из функционального генератора, логики ускоренного переноса и запоминающего элемента. Каждый КЛБ содержит четыре ЛЯ, организованные в виде двух одинаковых секций. В дополнение к четырем ЛЯ каждый блок содержит логику, позволяющую реализовывать функций от пяти или шести переменных.

В FPGA Spartan-II встроена особая блочная память большой емкости, созданная в дополнение к распределенной памяти небольшой емкости. Блоки памяти организованы в два столбца, расположенных вдоль каждой вертикальной стороны кристалла, при этом каждый блок памяти по высоте равен четырем КЛБ. Блок является полностью синхронным двухпортовым ОЗУ с независимым управлением для каждого порта.

В состав программируемой трассировочной матрицы входят локальные трассировочные ресурсы (ЛТР), трассировочные ресурсы общего назначения (ТРОН), трассировочные ресурсы для БВВ (ТРБ), специальные трассировочные ресурсы (СТР) и глобальные трассировочные ресурсы (ГТР). Первые позволяют реализовывать три типа соединений: связи между таблицами преобразования, триггерами и главной трассировочной матрицей (ГТМ — матрица переключателей); внутренние обратные связи КЛБ с таблицами преобразования в рамках одного КЛБ; прямые трассы для высокоскоростного соединения с соседними по горизонтали КЛБ. Большинство же связей в кристаллах реализуются с помощью ТРОН, расположенные в виде вертикальных и горизонтальных трассировочных каналов и расположенные в непосредственной близости от строк и столбцов матрицы КЛБ. ТРБ улучшают возможности закрепления сигналов за контактами и переназначения уже сделанного закрепления. СТР создавались для следующих видов сигналов: для реализации шин с тремя состояниями горизонтальные трассировочные ресурсы и для распространения сигналов быстрого переноса к прилегающему КЛБ две специальные линии в вертикальном направлении. ГТР распределяют сигналы с большим коэффициентом разветвления по выходу на всем пространстве кристалла, а также тактовые сигналы.

Поскольку БВВ поддерживает широкий спектр стандартов сигналов ввода-вывода, существуют возможности сопряжения кристаллов с большинством элементов памяти и шинных интерфейсов. БВВ содержит три запоминающих элемента, которые функционируют как триггеры-защелки или D-триггеры. Каждый БВВ имеет входной сигнал синхронизации, распределенный на три триггера и независимые сигналы разрешения тактирования. Для каждого из триггеров также заведен сигнал Сброса/Установки, который может быть сконфигурирован независимо, как синхронная установка, синхронный сброс, асинхронная предустановка или асинхронный сброс.

Входной сигнал БВВ может быть протрассирован через входной триггер или непосредственно к блокам внутренней логики. Каждый входной буфер может быть сконфигурирован таким образом, чтобы удовлетворять одному из стандартов ввода-вывода, поддерживаемых устройством. Выводной сигнал проходит через буфер с тремя состояниями, который подсоединен непосредственно к выводу микросхемы. Сигнал может быть протрассирован на вход буфера через выходной триггер блока ввода-вывода либо непосредственно от внутренней логической структуры.

В микросхему встроено четыре глобальных буфера, два — в середине верхней части микросхемы, два — в середине нижней части, которые проводят сигналы синхронизации на любой тактовый вход. Для каждого такого буфера имеется примыкающий к нему контакт микросхемы. На вход глобального буфера сигнал подается как с контактов, так и от сигналов ТРОН. Автоподстройка задержки (DLL) устраняет перекос задержек между сигналом на входном контакте микросхемы и сигналами на тактовых входах внутренних схем устройства.

Spartan-II поддерживает четыре режима конфигурирования: подчиненный последовательный, ведущий последовательный, подчиненный параллельный, периферийного сканирования.

Семейство состоит из шести кристаллов. В данной работе был использован XC2S200-PQ208. Характеристики данной ПЛИС представлены на табл. 1.

Таблица 1.

Характеристики кристалла XC2S200-PQ208.

Количество логических ячеек. | 5 292. | |

Количество системных вентилей. | 200 000. | |

Матрица КЛБ. | 28Ч42. | |

Количество КЛБ. | 1 176. | |

Число блоков памяти. | ||

Общий объем блочной памяти (бит). | 57 344. | |

Пользовательские блоки ввода-вывода. | ||

Объем конфигурационной последовательности (бит). | 1 335 840. | |

Вариант корпуса — максимальное число пользовательских контактов. | PQ-208 — 140. | |

2 Программное обеспечение Foundation Series.

Среда программирования Foundation Series (FS) фирмы Xilinx [15] позволяет производить полный цикл операций по разработке ПЛИС от ввода и отладки до программирования. Она поддерживает два способа проектирования: на языках описания аппаратуры (HDLs, Text-Based Entry) или схематично (Schematic, Schematic Entry) (Рис. 5).

В потоке HDL Flow проект содержит описания на VHDL, Verilog или описания на схемотехническом уровне, включающие модули написанные на VHDL или Verilog. Файлы на языках описания аппаратуры (HDL files) создаются с помощью встроенных редакторов: HDL Editor и Finite State Machine (FSM) Editor, также HDL-файл создается с помощью любого текстового редактора.

Необходимо отметить, что в данном потоке проектирования также используются модули на еще одном языке описания аппаратуры — XABEL (Xilinx ABEL). Эти модули, также как и LogiBLOX, CORE Generator (известные многим как XNF-файлы), используются для реализации проектов по методу черного ящика.

По способу реализации проекта (с помощью FPGAs или CPLDs) данный поток проектирования имеет два варианта, приведенные на рис. 6 и 7.

Отсюда видно, что языки описания аппаратуры в среде FS используются на следующих стадиях проектирования:

- 1. описание проектов (Design Entry);

- 2. моделирование с целью верификации проектов (Checkpoint Verification):

- — Функциональное моделирование трассировки — Gate-Level Functional Simulation;

- — Поведенческое моделирование HDL — Behavioral HDL Simulation;

- — Симуляция синхронизации по времени и времени трассировки — Post-Place&Route Gate-Level Timing Simulation;

- — Имитационное моделирование после этапа реализации трассировки — Post-Implementation Gate-Level Timing Simulation (опционально).

Основные пакетные модули FS:

- — Project Manager — графическое средство управления файлами проекта и основными модулями FS;

- — Synthesis Constraints Editor — редактор ограничений, накладываемых на проект, написанный на VHDL/Verilog, перед синтезом;

- — Synthesis Timing Analyzer — анализатор временных параметров синтезированных проектов;

- — Synopsys FPGA Express Synthesis — программа синтезирования проектов, написанных на VHDL/Verilog;

- — HDL Design Tools — набор утилит для упрощения ввода проекта на языках высокого уровня VHDL/Verilog, который включает в себя текстовый редактор, проверку синтаксиса, мастер готовых шаблонов основных конструкций языка, редактор диаграмм состояний;

- — ABEL Synthesis — модуль синтеза проектов, написанных на Abel;

- — Schematic Editor — графический редактор для ввода проектов в схемном виде на основе библиотек логических элементов;

- — Simulator — графический редактор, который позволяет моделировать до трассировки и после;

- — Design Manager — интерфейсный модуль для управления всеми средствами автоматической трассировки и дающий пользователю доступ к ним;

- — Flow Engine — модуль для отображения и выполнения этапов по размещению проекта в кристалл, которые состоят из трансляции входного файла универсального формата во внутренний формат, разбиения логики по конфигурируемым логическим блокам, размещения по кристаллу элементов логики и связей, создания конфигурационного файла для загрузки в кристалл, создания отчета о статических временных параметрах и создания файла для моделирования с учетом временных задержек в форматах VDHL, Verilog, EDIF или XNF;

- — LogiBLOX — графическое средство, позволяющее создавать параметризованные и оптимизированные под конкретную архитектуру логические элементы;

- — CORE Gen — модуль, который генерирует параметризованные и оптимизированные под конкретную архитектуру модули, выполняющие сложные функции;

- — Floorplanner — графическое средство для контроля процесса автоматического размещения логики в кристалл FPGA;

- — FPGA Editor — графическое средство для просмотра и редактирования результатов размещения логики и связей, а также проектирования вручную кристалла FPGA на уровне конфигурируемого логического блока и линий связи;

- — Hardware Debugger — программа загрузки и верификации проекта с компьютера;

- — PROM Files Formatter — программа создания конфигурационного файла для хранения в последовательных или параллельных ПЗУ.