Система синхронизации в микросхемах с высокой степенью интеграции

Применение драйверов, повышающих амплитуду синхросигнала позволяет установить оптимальный уровень синхросигнала для каждого функционального блока. При этом не требуются дополнительные источники и шины питания. Снижается общее число драйверов, используемых для распределения информации на кристалле микросхемы. Снижение напряжения питания микросхем, и повышение порогового напряжения МОП транзисторов… Читать ещё >

Система синхронизации в микросхемах с высокой степенью интеграции (реферат, курсовая, диплом, контрольная)

Развитие технологий производства микросхем направлено на увеличение степени интеграции, быстродействия и энергоэффективности. При этом снижается напряжение питания, устойчивость схемы к перегрузкам и помехам. В цифровых микросхемах система синхронизации имеет наибольшую длину проводников и распределена на всей площади кристалла. Соответственно, максимальная вероятность сбоя схемы определяется сбоеустойчивостью системы синхронизации. На сбоеустойчивость влияют выходное сопротивление драйверов синхронизации и логический перепад синхросигнала. Снижение выходного сопротивления драйверов может быть обеспечено двумя способами: увеличением ширины выходных КМОП транзисторов или повышением амплитуды сигнала, управляющего выходными транзисторами. Увеличение ширины выходных транзисторов значительно увеличивает площадь кристалла микросхемы и потребляемую мощность. Для повышения амплитуды управляющего сигнала необходимо введение в схему дополнительной шины электропитания или дополнительного каскада импульсного повышения амплитуды сигнала. В настоящей работе предложена схема драйвера синхросигнала с повышенной амплитудой управления выходными КМОП транзисторами.

Драйверы синхросигнала

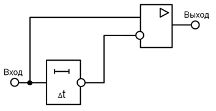

низковольтный синхросигнал драйвер амплитуда Драйвер импульсов с повышенной амплитудой включает два параллельных каскада (рис. 1а), управляемых входным сигналом с амплитудой равной напряжению питания.

Выходной импульс с повышенной амплитудой формируется срезом входного сигнала. Выходное напряжение повышается до уровня напряжения питания. Разделительный конденсатор Cp заряжается до напряжения равного (unum — uпор), где unum — напряжение источника питания, uпор — пороговое напряжение NМОП транзистора. Напряжение на выходе линии задержки повышается, когда NМОП транзистор в драйвере уже закрыт, PМОП открыт, а выходное напряжение достигло максимального уровня с учетом порогового напряжения NМОП транзистора. Напряжение на выходе продолжит повышение до уровня (2•unum — uпор).

Снижение напряжения питания микросхем, и повышение порогового напряжения МОП транзисторов с целью энергосбережения снижают эффективность импульсного повышения напряжения. Для дальнейшего повышения амплитуды управляющих импульсов предложено устройство, схема которого приведена на рис. 1б.

Рис. 1. — Формирователь импульсов с повышенной амплитудой

Повышение амплитуды импульсов осуществляется в два этапа. Для этого в устройстве используются две последовательно включенные линии задержки и три повышающих драйвера. На первом этапе две линии задержки и два драйвера формируют два сигнала с повышенной амплитудой, отличающиеся сдвигом во времени, соответствующим линии задержки. На втором этапе сигналы с повышенной амплитудой подаются на входы третьего повышающего драйвера. При этом амплитуда импульса выходного сигнала возрастает до величины (3•unum — 2•uпор).

На рис. 2 показаны результаты моделирования формы управляющих сигналов в режиме с нагрузкой в виде КМОП инвертора с суммарной шириной транзисторов 2 мм.

Отдельное внимание необходимо обратить на конструкцию разделительного конденсатора. Напряжение выходного сигнала драйвера зависит от соотношения емкостей разделительного конденсатора и нагрузки драйвера. Емкость нагрузки определяется суммарной шириной транзисторов, управляемых одним драйвером. Эффективность повышения напряжения достигается в случае, если емкость разделительного конденсатора превышает емкость нагрузки не менее, чем в 3 ч 5 раз.

1 — входной сигнал; 2 — выходной сигнал после первого этапа преобразования; 3 — выходной сигнал после второго этапа преобразования.

В традиционной технологии, использующей планарные конденсаторы с изоляцией электродов оксидом кремния, площадь разделительных конденсаторов может превышать площадь управляемых ключевых транзисторов [1]. В современных технологиях конденсаторы реализуются на основе многослойных структур с использованием диэлектриков с высокой диэлектрической проницаемостью (более 20), что снижает площадь конденсаторов в 5 ч 7 раз. Диэлектрики с высокой диэлектрической проницаемостью являются неотъемлемой частью современных КМОП технологий и используются не только в транзисторных структурах.

Исключение дополнительного источника питания и уменьшение размеров выходных транзисторов оценено авторами как уменьшение активной площади кристалла на 0,5 ч 1 мм2, и соответствующее упрощение конструктивных решений при применении изделий.

Заключение

Применение драйверов, повышающих амплитуду синхросигнала позволяет установить оптимальный уровень синхросигнала для каждого функционального блока. При этом не требуются дополнительные источники и шины питания. Снижается общее число драйверов, используемых для распределения информации на кристалле микросхемы.

- 1. Круглов Ю. В. Интеграторы на переключаемых конденсаторах для широкополосных сигма-дельта модуляторов с большим динамическим диапазоном // дис. … канд. тех. наук: 05.27.01. М.: МИЭТ, 2005. 153 с. URL: tekhnosfera.com (дата обращения: 18.04.2017).

- 2. Документация на микросхемы фирмы SANYO LA 7837, LA 7838 // MONITOR URL: master-tv.com (дата обращения: 18.04.2017).

- 3. Лубков А. А., Перебейнос С. В., Зотов А. А., Котов В. Н., Лылов С. А. Источник высокого знакопеременного напряжения, программируемого по амплитуде и частоте // Патент на полезную модель № 120 297 по заявке № 2 012 118 341, приоритет 03.05.2012 г.

- 4. M. Dessouky and A. Kaiser «Very Low-Voltage Digital-Audio AS Modylator with 88 dB Dynamic Range Using Local Switch Bootstrapping», IEEE J. Solid-State Circuit, vol. 36, no. 3, March 2001, pp. 349−355.

- 5. A. Ong, V. Prodanov, M. Tarsia «A metod for reducing the variation in „ON“ resistance of a MOS sampling switch», submitted to IEEE International Symposium on Circuits and Systems, Geneva, 2000, May 28−31, pp. 437−440.

- 6. Белоус В., Дрозд С., Листопадов А. Схемотехнические методы повышения помехоустойчивости цифровых КМОП микросхем // Компоненты и технологии, 2010, № 6, C. 132−137.

- 7. Адамов Ю. Ф., Балака Е. С., Рухлов В. С. Схемотехника электронных устройств, работающих в условиях электромагнитных помех // Материалы конференции МЭС-2016, Москва, 2016, C. 14−19.

- 8. Д. В. Тельпухов, В. С. Рухлов, И. С. Рухлов Исследование и разработка методов оценки сбоеустойчивости комбинационных схем, реализованных в базисе ПЛИС // Инженерный вестник Дона, 2016, № 1 URL: ivdon.ru/ru/magazine/archive/n1y2016/3504/.

- 9. С. Ф. Тюрин, Городилов А. Ю., Данилова Е. Ю. Диагностирование логического элемента DC LUT FPGA // Инженерный вестник Дона, 2014, № 2 URL: ivdon.ru/ru/magazine/archive/n2y2014/2313/.

- 10. R.E. Bryant, Kwang-Ting Cheng, A.B. Kahng «Limitation and challenges of computer-aided design technology for CMOS VLSI», Proceedings of the IEEE, vol. 89, no. 3, Mar 2001, pp. 341−365.

- 11. Волобуев С. В. Параллельно-конвейерная процедура и устройство распределенной барьерной синхронизации матричных СБИС мультикомпьютеров // дис. … канд. тех. наук: 05.13.05. Курск: ЮЗГУ, 2010. 151 с. URL: tekhnosfera.com (дата обращения: 04.05.2017).