Основные виды микросхем статической памяти

Все сигналы, кроме сигнала управления выходными буферами ОЕ#, синхронизируются по положительному перепаду сигнала CLC. Микросхемы Sync Burnt SRAM обычно имеют сигнал, выбирающий режим счета адреса: чередование (для процессоров Intel) или последовательный счет (для Power PC). Микросхемы обеспечивают временную диаграмму 2−1−1−1 на частотах работы системной шины 50, 60 и 66 МГц и имеют время доступа… Читать ещё >

Основные виды микросхем статической памяти (реферат, курсовая, диплом, контрольная)

Асинхронная статическая память («Asynchronous SRAM — Async SRAM или просто SRAM,) до недавних пор являлась стандартной памятью и ей не было альтернативы. Интерфейс микросхем этой памяти включает шину адреса, шину данных и следующие сигналы управления (с нулевым активным уровнем):

- • сигнал выборки кристалла (Chip Select — CS), активизирующий микросхему при CS# = 0, где # - знак инверсии. При объединении микросхем внутренний сигнал CS# может быть получен из нескольких внешних (например, CSO#, CS1# и CS2#) с использованием схемы И;

- • сигнал разрешения вывода (Output Enable — ОЕ), открывающий при OE# = 0 выходные буферы для считывания данных;

- • сигнал разрешения записи WE# (Write Enable — WE) при WE# = 0. При операции записи управление выходными буферами может производиться как сигналом ОЕ#, так и сигналом WE#. Время доступа, представляющее собой задержку появления действительных данных на выходе относительно момента установления адреса, для стандартных микросхем SRAM составляет 12, 15 или 20 нс. Это позволяет процессору выполнять пакетный цикл чтения 2−1-1−1 на частоте системной шины до 33 МГц. На более высоких частотах формула цикла имеет вид 3−2-2−2. При использовании статической памяти в кэше процессор посылает адрес, после чего кэш производит поиск адреса и передает требуемые данные. В начале каждого обращения, как правило, используется дополнительный цикл для просмотра тегов. В этом случае групповая операция чтения данных описывается формулой 3−2-2−2, а операция записи — формулой 4−3-3−3 [6, 7].

Синхронная пакетная статическая память (Sync Burst SRAM) предназначена для пакетных операций обмена в кэш-памяти. Микросхема памяти содержит дополнительно 2-битный счетчик адреса, не позволяющий перейти границу 4-элементного пакетного цикла, а помимо сигналов CS#, OE# и WE# для синхронизации с системной шиной используются сигнал CLC (Clock) и сигналы управления пакетным циклом, при этом:

- • сигналы CADS# (Cache ADdress Strobe) и ADSP# (ADdress Status of Processor) являются стробами записи начального адреса цикла во внутренний регистр адреса. Этими сигналами процессор или кэшконтроллер отмечает фазу адреса очередного цикла. Любой из них инициирует одиночный или пакетный цикл обращения;

- • сигнал ADV# (ADVance) используется для перехода к следующему адресу пакетного цикла.

Все сигналы, кроме сигнала управления выходными буферами ОЕ#, синхронизируются по положительному перепаду сигнала CLC. Микросхемы Sync Burnt SRAM обычно имеют сигнал, выбирающий режим счета адреса: чередование (для процессоров Intel) или последовательный счет (для Power PC). Микросхемы обеспечивают временную диаграмму 2−1-1−1 на частотах работы системной шины 50, 60 и 66 МГц и имеют время доступа 8,5, 10 и 13,5 нс соответственно. На частотах 75 МГц и выше формула чтения блока данных имеет вид 3−2-2−2.

Конвейеризированная пакетная память (Pipelined Burst SRAM — РВ SRAM), поддерживающая конвейерный режим выполнения групповых операций чтения/записи, является дальнейшим усовершенствованием синхронной памяти. Конвейеризация реализуется добавлением выходного буфера, в который помещаются считанные из ячеек памяти данные. Буфер обеспечивает более быстрый доступ к данным при последовательных обращениях по чтению из памяти, так как не требуется обращение к матрице памяти для получения следующего элемента данных. Буферный регистр использует дополнительные такты только в пересылке первого элемента данных пакета, остальные элементы следуют без тактов ожидания. Память микросхем РВ SRAM обеспечивает временную диаграмму 3−1-1−1 на частотах 66, 75 и 83 МГц (время доступа 15, 13 и 12 нс соответственно). Задержка данных относительно синхронизирующего перепада у современных микросхем составляет 4,5…8 нс [2].

Таким образом, микросхемы статической памяти имеют:

- • сравнительно высокое быстродействие;

- • большие размеры и стоимость микросхем из-за большого количества транзисторов и кластеризованного их размещения. В частности, при емкости модуля DRAM 64 Мбайт емкость модуля SRAM такого же размера составляет порядка 2 Мбайт, при этом модули имеют одинаковую стоимость. Следовательно, габариты и стоимость SRAM примерно в 30 раз превышают аналогичные показатели оперативной памяти. По этой причине SRAM не находит применения в качестве оперативной памяти в персональных компьютерах.

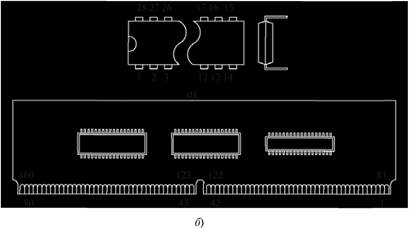

Конструктивное исполнение. Микросхемы асинхронной памяти обычно исполняются в DIP-корпусах с 8-битной организацией (рис. 9.1,а) и устанавливаются в специальные «кроватки» системной платы. Банк для процессоров Pentium собирается из 4 микросхем. Микросхемы синхронной памяти имеют разрядность 16 или 32 бита (18 или 36 — с паритетом), один банк для Pentium собирается из 4 или 2 микросхем.

Рис. 9.1. Корпус DIP-28 и модуль кэш-памяти COPAST.

Модули кэш-памяти содержат микросхемы статической памяти (Async SRAM, Sync Burst SRAM или PB SRAM) необходимой разрядности. На плате модуля может быть также установлена асинхронная память тегов. Для системных плат с сокетами были распространены модули COAST (Cache On A Stick — кэш на палочке) с двусторонним печатным разъемом (рис. 9.1,6), устанавливаемым в специальный слот. В результате снижения цен на микросхемы статической памяти кэш стали запаивать на системную плату, не применяя дополнительных модулей и разъемов.