Перспективные направления развития элементной базы сверхбольших интегральных схем

На рис. 21.23 показан один из вариантов транзистора с трехмерной структурой затвора. Канал сток — исток выступает над поверхностью подложки в виде плавника (как плавник акулы над водной поверхностью), а затвор охватывает его с трех сторон (как подкова). Объемный транзистор, представленный на рис. 21.23, получил название полевой транзистор с плавником {field effect transistor — FinFET). Одним… Читать ещё >

Перспективные направления развития элементной базы сверхбольших интегральных схем (реферат, курсовая, диплом, контрольная)

Развитие элементной базы в современной электронике происходит по двум основным направлениям.

- 1. Увеличение степени интеграции СБИС, снижение их энергопотребления и повышение функциональной сложности за счет перехода от планарной (2D) технологии производства МОП-транзисторов к объемной (3D) технологии.

- 2. Использование новых физических явлений (в том числе приборов с зарядовой связью) и материалов.

Остановимся подробнее на каждом из названных направлений.

Повышение степени интеграции и снижение энергопотребления сверхбольших интегральных схем

Энергопотребление МОП-транзисторов можно снизить за счет уменьшения размера и усовершенствования их структуры. Поэтому задача увеличения степени интеграции и снижения энергопотребления СБИС решалась и решается в настоящее время путем ужесточения так называемых топологических (технологических) норм. Под топологической нормой (ТН) понимаются минимально возможные размеры при изготовлении каждой отдельной области полупроводника с заданным типом проводимости. В диоде и тем более транзисторе таких областей несколько. Поэтому размеры этих элементов превышают ТН.

Оборудование и технология производства СБИС с ТН в диапазоне от 5—10 до 100 нм имеют специфические особенности и в настоящее время выделены из микроэлектроники в самостоятельную стремительно развивающуюся отрасль науки и техники — наноэлектронику [11.15]. Нижняя граница названного диапазона точно не определена и соответствует переходу от современной нанотехнологии проектирования СБИС [Д.2] к технологии будущего [Н.19].

Отечественным производством освоен технологический уровень 90 нм и активно разрабатываются технологии 65—45 нм [Д.2].

При ТН менее 100 нм в планарных (плоскостных) структурах полупроводника из-за неизбежного укорочения проводящего капала в МОП-трапзисторах резко возрастает утечка части зарядов из канала в подложку. Уменьшить ток утечки удалось путем изоляции канала сток — исток от подложки тонким слоем специального диэлектрика с высоким значением диэлектрической константы (технология кремния на изоляторе). Новая технология позволила фирме Intel освоить в производстве СБИС микропроцессоров с ТН 45 нм в 2007 г. и 32 нм в 2009 г.

Одним из перспективных путей дальнейшего снижения ТН до 14—22 нм стал переход от планарной (2D) технологии изготовления МОПи КМОПтранзисторов к объемной (3D) технологии. Такой переход оказался возможным лишь потому, что предварительно были тщательно изучены электромагнитные процессы в объемных транзисторах и построены соответствующие расчетные модели.

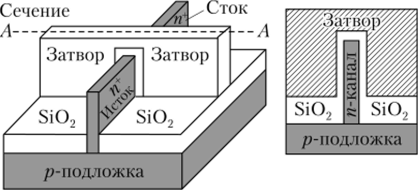

На рис. 21.23 показан один из вариантов транзистора с трехмерной структурой затвора. Канал сток — исток выступает над поверхностью подложки в виде плавника (как плавник акулы над водной поверхностью), а затвор охватывает его с трех сторон (как подкова). Объемный транзистор, представленный на рис. 21.23, получил название полевой транзистор с плавником {field effect transistor — FinFET).

Разновидностью объемного транзистора (см. рис. 21.23) является его трехнлавниковый вариант, имеющий три выступающих над поверхностью подложки канала — плавника. Их охватывает общий (трехиодковообразный) затвор. Такие транзисторы называются трехзатворными {Fn-Gate).

Рис. 21.23. МОП-транзистор с трехмерной структурой затвора и канала в виде плавника (FinFET):

а — общий вид транзистора; б — поперечное сечение (А—А)

В 2013 г. фирма Intel выпустила СБИС микропроцессора с применением трехзатворных объемных транзисторов. Важно отметить, что этот микропроцессор изготовлен по технологии с топологическими нормами (ТН) 22 нм [22].

В конце 2013 г. фирмами Altera и ХШпх объявлено о начале поставок нового поколения микросхем программируемой логики, выполненных по технологии с ТН 20 нм [26, 29]. Емкость ППВМ Virtex UltraScale фирмы Xilinx теперь превышает 4 млн эквивалентных (простейших) логических ячеек!

Фирмой Altera предполагается выпуск нового (десятой модификации) семейства высокопроизводительных СБИС программируемой логики Altera Stratix 10 но революционной технологии Intel с топологическими нормами 14 нм [27].

Переход на объемные транзисторы позволил понизить напряжение питания ППВМ до 2,5—3 В. Кроме того, дальнейшее снижение порогового напряжения новых нолевых транзисторов U (уровня логической «единицы» на входе) является дополнительным способом уменьшения энергопотребления СБИС. В частности, фирма Intel поставила перед собой задачу понижения [/пор до 0,3—0,5 В и уменьшения потребляемой энергии всей СБИС в нерабочем состоянии до уровня, не превышающего 1 мВт [22].