Десятичные сумматоры.

Электроника и схемотехника

Пример 2. При сложении одноразрядных десятичных чисел (5 + 8 = 13) получен результат 1101 (1310) в виде 4-разрядного двоичного числа, превышающего число 9. При проведении коррекции путем прибавления числа 0110 (610) получим сумму 10 011 (1910) в виде 5-разрядного числа. Пятый разряд «уходит» в старшую тетраду, забирая с собой 16 единиц, и оставляет правильный результат 0011 (Зш). Таким образом… Читать ещё >

Десятичные сумматоры. Электроника и схемотехника (реферат, курсовая, диплом, контрольная)

Многоразрядные десятичные сумматоры строятся на основе одноразрядных десятичных сумматоров.

Одноразрядные десятичные сумматоры. Для суммирования двух одноразрядных десятичных чисел используют двоичные сумматоры. При этом десятичное одноразрядное число представляют в виде 4-разрядного двоичного кода — тетрады. Для представления положительных десятичных чисел используют код 8421, код с избытком 3 и др.

Рассмотрим один из возможных способов суммирования положительных одноразрядных десятичных чисел, представленных в коде 8421, и его схемную реализацию.

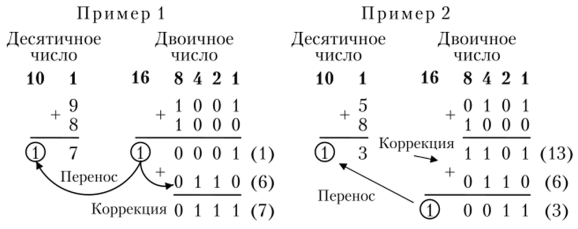

Сложение тетрад происходит по правилам двоичной арифметики. Если сумма больше 9, то возникает необходимость в проведении коррекции. Значение суммы от 10 до 19 единиц (1010, 1011,…, 10 011) выявляется по следующим признакам:

- • появление при суммировании пятого разряда двоичного числа в виде переноса в следующую тетраду (числа от 10 000 до 10 011);

- • наличие единиц в разрядах с весом 8 и 2 (числа 1010 и 1011), 8 и 4 (числа от 1100 до 1111).

Коррекция осуществляется дополнительным прибавлением двоичного числа ОНО (6|0) к полученному результату. Это обусловлено тем, что вес пятого разряда двоичного числа составляет 16 десятичных единиц, а вес старшего разряда десятичного числа — 10, т. е. разность равна 6. Поясним принцип коррекции па двух примерах. Предполагается, что значение переноса из предыдущей тетрады равно 0.

Пример 1. При сложении одноразрядных десятичных чисел (9 + 8 = 17) получен результат 10 001 в виде 5-разрядного двоичного числа. Значение 1 в пятом разряде соответствует 16 в десятичном исчислении. После переноса единицы пятого разряда в старшую тетраду ее значение становится равным 10. Так как перенос сопровождается уменьшением результата па 6 десятичных единиц, к тетраде необходимо прибавить двоичное число ОНО (610).

Пример 2. При сложении одноразрядных десятичных чисел (5 + 8 = 13) получен результат 1101 (1310) в виде 4-разрядного двоичного числа, превышающего число 9. При проведении коррекции путем прибавления числа 0110 (610) получим сумму 10 011 (1910) в виде 5-разрядного числа. Пятый разряд «уходит» в старшую тетраду, забирая с собой 16 единиц, и оставляет правильный результат 0011 (Зш). Таким образом, в этом случае преднамеренная коррекция вызвала появление единицы в пятом разряде, перенос которой в следующую тетраду позволил получить правильный результат.

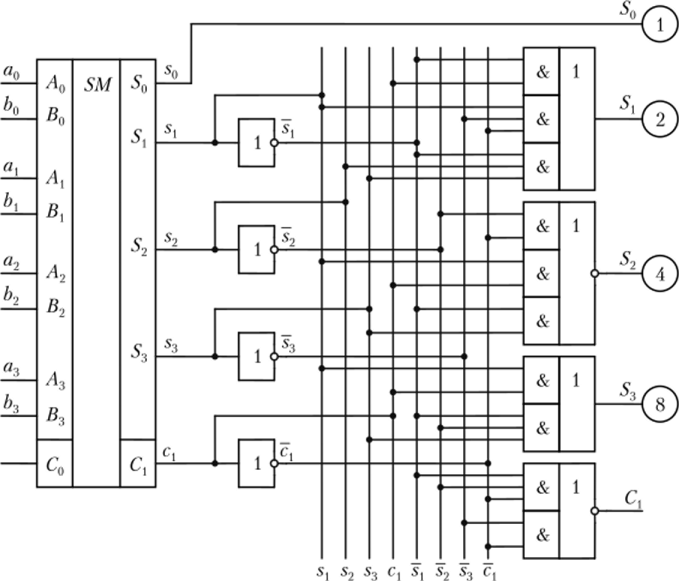

На рис. 9.79 приведена схема одноразрядного десятичного сумматора с коррекцией результатов сложения входных операндов.

Схема содержит:

• 4-разрядный сумматор. На его вход поступают одноразрядные десятичные числа в виде двух тетрад АъА2А{Ай, В3В2В1В0 и перенос С0 из предыдущей тетрады. С выхода сумматора снимается 4-разрядная сумма и перенос с4 в следующую тетраду;

- • формирователь переноса С, в следующую тетраду, выполненный на трех логических элементах. Перенос С, = 1, если с4 = 1, или 53 = 52= 1, или 53 = 5, = 1;

- • корректор результата, построенный на трех одноразрядных двоичных сумматорах. Так как при коррекции прибавляется 4-разрядное двоичное число 0110, младший разряд которого равен 0, одноразрядный двоичный сумматор младшего разряда не используется, на вход переноса сумматора 5М-1 подается сигнал переноса С, = 0, а один из входов сумматора 5М-3 старшего разряда — логический нуль. На один вход одноразрядных двоичных сумматоров

Рис. 9.79. Одноразрядный десятичный сумматор с коррекцией подастся сигнал .ък(к — 1, 2, 3) с выхода 4-разрядного сумматора, на другой вход сумматоров 5М-1 и 5М-2 — сигнал С, с выхода формирователя переноса. При С, = 1 полученный на выходе 4-разрядного сумматора результат корректируется. При С1 = 0 коррекции не происходит, с выхода десятичного сумматора снимают выходные сигналы 4-разрядного сумматора.

Отметим, что для строгости изложения следовало бы в обозначения сигналов ввести индекс г (например, Л-3), свидетельствующий о том, что речь идет о десятичном сумматоре ?-го разряда. Однако он опущен, чтобы упростить обозначения.

Известен другой способ суммирования положительных десятичных чисел, не требующий проведения коррекции результата, полученного на выходе 4-разрядного сумматора. Для его обоснования воспользуемся табл. 9.28.

Таблица 9.28

п | Выходные сигналы. | п | Выходные сигналы. | ||||||||||||||||||

двоичного сумматора. | десятичного сумматора. | двоичного сумматора. | десятичного сумматора. | ||||||||||||||||||

С1. | *3. | $ 2. | 50. | С,. | л; | ?*,. | •*о. | С1. | *3. | $ 2. | 50. | С,. | .V,. | 52 | •*,. | ?*0. | |||||

В первой графе (п) табл. 9.28 представлены в десятичной системе счисления все числа, которые могут быть получены на выходе 4-разрядного сумматора при сложении одноразрядных чисел от О до 9 с учетом входного переноса с0= 1. Максимальное число равно 9 + 9+1 = 19. В последующих пяти графах эти же числа записаны в виде 5-разрядных двоичных чисел, которые могут быть получены как выходные сигналы переноса с, и суммы $3, $2, 50 4-разрядного двоичного сумматора. В правых частях табл. 9.28 десятичные числа от 0 до 19 записаны в том виде, который они должны иметь на выходе одноразрядного десятичного сумматора, а именно, в виде сигнала переноса С1 и кода 8421 (5352515,0). Отметим, что перенос С1 отражает значения старшего разряда, а код — значения младшего разряда двухразрядиого десятичного числа. Для схемной реализации одноразрядного десятичного сумматора необходимо синтезировать комбинационную схему, преобразующую приведенные в табл. 9.28 выходные сигналы двоичного сумматора с, 53, 52, 51, 50в требуемые сигналы С, $3, 52, 5, 50. Из табл. 9.28 очевидно, что 50 = 50. Поэтому задача синтеза упрощается: необходимо построить комбинационную схему на четыре входа (с, 53, 52, 5,) и четыре выхода (С, 53, 52, 5,), используя при этом девять наборов входных переменных, так как при п, равном 0 и 1,2 и 3,4 и 5 и т. д., одноименные входные переменные имеют одинаковые значения.

Для синтеза комбинационной схемы преобразователя воспользуемся таблицей истинности (табл. 9.29).

Таблица 9.29

Входы. | Выходы. | Входы. | Выходы. | ||||||||||||||

С1. | 5з. | 52. | *1. | С. | •*з. | 52 | 5. | С1. | *3. | 62. | *1. | С,. | ^3. | 52 | |||

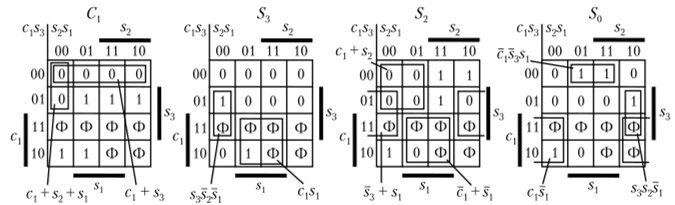

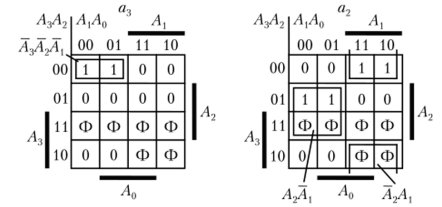

На основании табл. 9.29 выполним минимизацию выходных сигналов с помощью карт Карно, как неполностью определенных функций. На рис. 9.80 приведены размеченные карты и выражения для выделенных областей. В результате минимизации получаем следующие структурные формулы для комбинационной схемы 11 реобразователя:

Схема одноразрядного десятичного сумматора с преобразователем, построенным по приведенным структурным формулам, изображена на рис. 9.81.

Рис. 9.80. Карты Карно для минимизации структурных формул схемы преобразователя.

Рис. 9.81. Одноразрядный десятичный сумматор с преобразователем кодов.

Десятичный одноразрядный вычитателъ. Для вычисления разности двух положительных одноразрядных чисел или алгебраической суммы чисел с разными знаками необходимо использовать операцию преобразования прямого кода 8421 в обратный код 8421. Такая операция часто называется преобразованием кода 8421 в дополнение до 9 и выполняется в соответствии с табл. 9.30.

Таблица 930

Число. | Прямой код 8421. | Обратный код 8421. | ||||||

«10. | а2 | Л. | Л. | с12 | 4). | |||

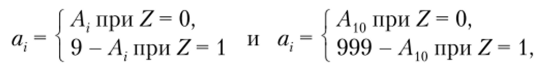

Из^ сопоставления столбцов табл. 9.30 следует, что с10 = Лц, <3Х = Л,. Выражения для Л2 и Л3 получены с помощью карт Карно (рис. 9.82). Ниже приведены структурные формулы для преобразователя кода 8421 в дополнение до 9:

Рис. 9.82. Карты Карно для получения выражений выходных сигналов а3 и а.2 преобразователя кода 8421 в дополнение до 9.

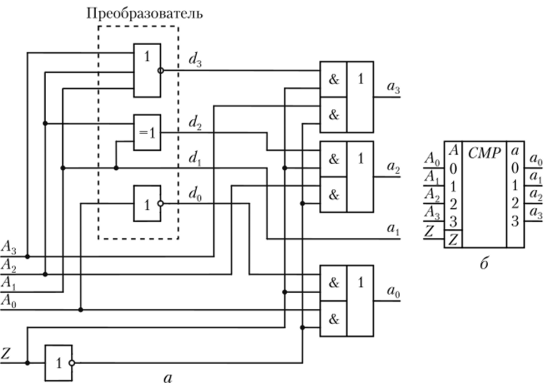

Выпускаемые в интегральном исполнении преобразователи строят по приведенным выше структурным формулам и дополняют их входом управления. Схема управляемого преобразователя кода 8421 в дополнение до 9 (CMP — complement) и его условное графическое обозначение представлены на рис. 9.83.

Рис. 9.83. Управляемый преобразователь прямого кода 8421 в обратный код (я) и его условное графическое обозначение (б).

Управляемый преобразователь содержит:

- • преобразователь кода 8421 в дополнение до 9 (выделен на рис. 9.83, а пунктирной линией), построенный, но формулам (9.60);

- • мультиплексоры 2 —? 1 для нулевого, второго и третьего разрядов входного операнда Л, состоящие из инвертора и трех элементов 2И-ИЛИ. Наличие трех вместо четырех мультиплексоров обусловлено тем, что первый разряд входного операнда не изменяет значения при прохождении преобразователя, т. е. сигнал на выходе управляемого преобразователя ал = Л, = (1х.

При 2= 0 открыты верхние схемы совпадения элементов 2И-ИЛИ, и на их выход проходят сигналы ?/3, ?/2, ?/0 обратного кода 8421. При 2 = 1 открыты нижние схемы совпадения, и на выход поступают сигналы отдельных разрядов Л3, Л.;, Л0 входного операнда.

На рис. 9.84 приведена схема 3-разрядного десятичного сумматора-вычитателя, содержащего три управляемых преобразователя СМРх десятичного числа в дополнение до 9 и три одноразрядных десятичных сумматора 5 М, (/ = 0, 1, 2). Значение управляющего сигнала Z= 0 соответствует операции сложения, а 2 = 1 — операции вычитания. Преобразователи СМРх выполняют функции.

где

а{> Л; — 4-разрядные операнды (тетрады) на выходах и входах управляемых преобразователей:

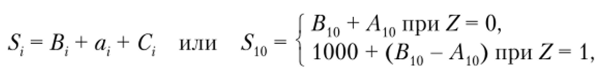

Десятичные сумматоры вычисляют сумму.

где 5, = ЗДЗД; = ^8|2^пДо' С, ~ сигнал переноса на входе ?-го сумматора, причем С0 = 2; В10, Л10, 5,10 — входные операнды и сумма в десятичной системе счисления.

При вычитании (2=1) сумма представляется в десятичном дополнительном коде и может иметь положительное или отрицатель;

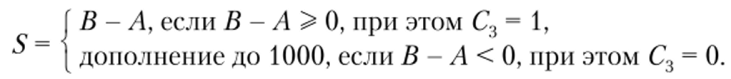

Рис. 9.84. Схема 3-разрядного десятичного сумматора-вычитателя ное значение. Значение и знак суммы определяются по значению сигнала переноса С3 и имеют следующий вид:

Знаковым разрядом является перенос С3. Чтобы при сложении разрядная сетка не переполнялась, должно выполняться условие В + А <999.

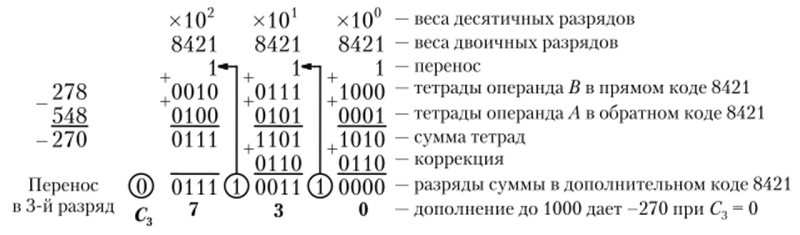

Изложенный принцип работы сумматора-вычитателя проиллюстрирован на трех примерах.

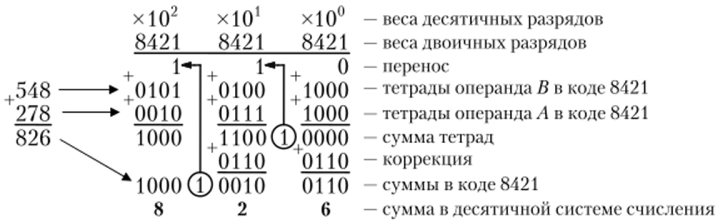

Пример 1. Суммирование 3-разрядных положительных десятичных чисел (В10 + Л10).

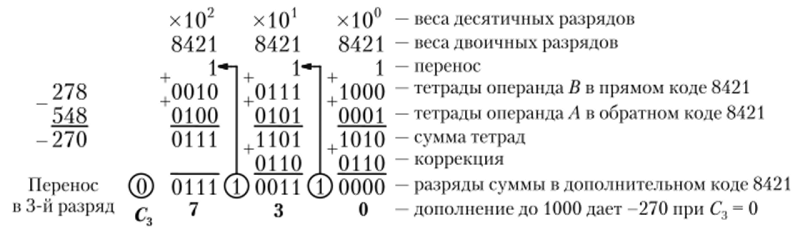

Пример 2. Вычитание трехразрядных положительных десятичных чисел (В10- Л10>0).

Пример 3. Вычитание трехразрядных положительных десятичных чисел (Bi0 — Л10 < 0).