Синхронные триггеры.

Электроника и схемотехника

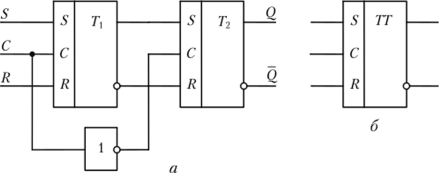

Рис. 10.7. Схемы D-триггера с включением инвертора между информационными входами синхронного Я5-триггера (а), с минимальным числом логических элементов (б) и его условное обозначение (в) нения S- и /?входов синхронного /?S'-триггера через инвертор. При таком соединении на информационные входы /?S'-триггера никогда не поступает не только запрещенная комбинация сигналов (S = R = 1), но и комбинация… Читать ещё >

Синхронные триггеры. Электроника и схемотехника (реферат, курсовая, диплом, контрольная)

Синхронные Л^-триггеры имеют дополнительный С-вход для подачи управляющих (тактовых, синхронизирующих) импульсов, под действием которых происходит изменение их состояния. Сигналы на информационные .9- и У?-входы выставляются до подачи синхроимпульса. Синхронные У?5-триггеры строят по одноступенчатой и двухступенчатой схемам.

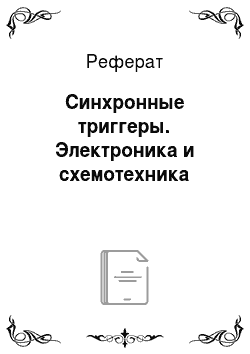

Для построения одноступенчатого синхронного У?5-триггера на входе его асинхронного аналога достаточно включить два логических элемента. Схема такого триггера с использованием логических элементов И-НЕ и его обозначение приведены на рис. 10.5.

Рис. 10.5. Одноступенчатый синхронный /?5-триггер на элементах И-НЕ (а) и его условное обозначение (б)

При С = 0 независимо от состояния информационных 5- и /?-входов на выходах логических элементов формируются сигналы 5 = = /? = 1, при которых асинхронный триггер находится в режиме хранения (ем. табл. 10.3). При С = 1 оба логических элемента открыты, и асинхронный триггер реагирует на все разрешенные комбинации сигналов, поступающих на 5- и /?-входы.

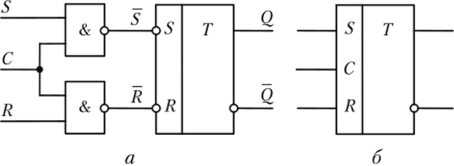

Двухступенчатые триггеры реализуются, но схеме ведущий — ведомый. Занесение информации в триггер разделено во времени: вначале информация записывается в первую ступень, а затем переписывается во вторую. На рис. 10.6 приведены вариант схемы, наиболее доступный для понимания принципа работы двухступенчатого /?5-триггера, а также условное обозначение двухступенчатого синхронного триггера.

В схеме на рис. 10.6, а использованы два синхронных /?5-триггера и инвертор. При С= 1 производится запись информации в триггер Г, триггер Г2 находится в режиме храпения (заблокирован), так как на его С-вход через инвертор подается нулевой сигнал. При С = 0 блокируется триггер Гр па С-вход триггера Г2 поступает единичный сигнал, и информация с выхода триггера Г, переписывается на выход триггера Г2.

Рис. 10.6. Двухступенчатый синхронный /?5-триггср с инвертором (а) и его условное графическое обозначение (б).

Следует отметить, что:

- • запись информации (появление ее на выходе) в двухступенчатые триггеры происходит по срезу (при изменении из 1 в 0) входного синхроимпульса, т.с. с задержкой на длительность синхроимпульса;

- • в двухступенчатых триггерах отсутствует прямая связь между входом и выходом, так как всегда какая-то одна из его ступеней находится в режиме хранения. Поэтому двухступенчатые триггеры устойчиво работают при наличии обратных связей, которые используются при построении рассматриваемых ниже Ги //?-триггеров.

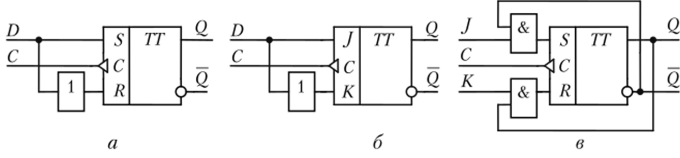

//-триггеры. Один из способов устранения недостатка /?5-триггеров — наличия запрещенной комбинации входных сигналов — приводит к //-триггерам. На рис. 10.7, а приведена схема О-трштера, в которой запрещенная комбинация исключается путем соеди;

Рис. 10.7. Схемы D-триггера с включением инвертора между информационными входами синхронного Я5-триггера (а), с минимальным числом логических элементов (б) и его условное обозначение (в) нения S- и /?входов синхронного /?S'-триггера через инвертор. При таком соединении на информационные входы /?S'-триггера никогда не поступает не только запрещенная комбинация сигналов (S = R = 1), но и комбинация S = R = 0, соответствующая режиму хранения, который реализуется путем подачи С= 0. Другой возможный вариант схемного решения D-триггера с меньшим количеством логических элементов показан на рис. 10.7, б. Этот D-триггер построен на основе синхронного /?S'-триггера (см. рис. 10.5, а), в котором внешний /?вход подключен к внутреннему 5-входу асинхронной части триггера. На рис. 10.7, в приведено условное графическое обозначение D-триггера.

По выполняемым функциям D-триггеры не отличаются от синхронных /?S'-триггеров, однако имеют один информационный Dвход. Поскольку в D-триггерах задерживается прохождение входного сигнала на выход схемы до появления синхроимпульса, их также называют триггерами задержки (delay).

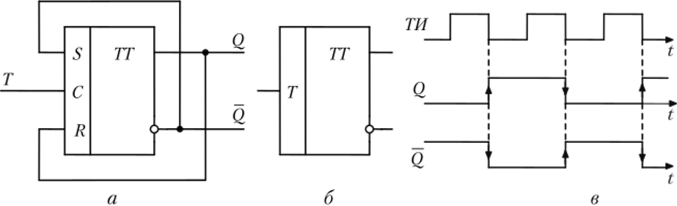

Г-триггеры. Эти триггеры представляют собой устройства с единственным входом, на который поступают тактовые импульсы (ТИ). Каждый тактовый импульс изменяет состояние триггера на инверсное.

Основой для построения Г-триггеров могут служить двухступенчатые синхронные RS-триггеры, в которых для изменения состояния триггера на инверсное используются собственные выходные сигналы. При этом инверсный Q-выход триггера соединяется с 5-входом, а прямой Q-выход — с /?входом триггера (рис. 10.8, а). На рис. 10.8, б приведено условное графическое обозначение Г-триггера. Так как появление сигнала на выходе двухступенчатого триггера задерживается на время действия тактового импульса (при Т = 1 вторая ступень заблокирована), изменение состояния (переключение) 7-триггера происходит по срезу тактовых импульсов. Эта особенность отражена на временных диаграммах (рис. 10.8, в). Правила его работы: при поступлении Тк = 0 триггер сохраняет предыдущее состояние Qk~ а при поступлении Тк = 1 он изменяет предыдущее состояние на инверсное Qk л.

Рис. 10.8. Схема Г-триггера, построенная на основе двухступенчатого синхронного /?5-триггера (а), его условное графическое обозначение (б) и временные диаграммы, иллюстрирующие выполняемые Г-триггером функции (в).

/К-триггеры. Второй способ устранения недостатка /^-триггеров — наличия запрещенной комбинации входных сигналов — приводит к ]К-триггерам. В у/С-триггерах запрещенная для ^'-триггеров комбинация используется в полезных целях: при этой комбинации входных сигналов у/С-триггер работает как Г-триггер.

у/С-триггеры могут быть построены двумя равноценными способами:

- • на основе двухступенчатых синхронных /?5-триггеров путем создания условий для инверсного (тактируемого) режима при запрещенной комбинации;

- • па основе Г-триггеров путем создания двух дополнительных входов для управления состоянием выходов.

Рассмотрим первый способ, взяв за основу двухступенчатый синхронный /?5-триггер. Если в первой ступени Г, использовать логические элементы И-НЕ с тремя входами, а дополнительные входы задействовать для организации обратных связей, как в Г-триггере, то после переименования информационных входов Я, 5 на у, К получим схему у/С-триггера, которая приведена на рис. 10.9, а. Условное графическое обозначение у/С-триггера показано на рис. 10.9, б.

При трех комбинациях входных сигналов (У = К = 0; У = 1, К = 0 и у = 0, К = 1) у/С-триггер выполняет функции /?5-триггера, т. е. обратные связи не оказывают влияния на его работу. Действительно:

- • при комбинации у = /С = 0 с выходов логических элементов 1 и 2 на входы первого триггера поступают сигналы Б = Я = 1, соответствующие режиму хранения;

- • комбинация У = 1, К = 0 при С = 1 соответствует режиму записи 1. В это^ режиме на выходе логического элемента 2 формируется сигнал Я = 1. На выходе элемента 1 сигнал зависит от предшествующего состояния триггера. Если триггер находился в нулевом состоянии ((2 = 0), то 5 = 0, так как на все входы элемента 1 поступают единичные сигналы. В этом случае в триггер записывается 1. Если же триггер находился в единичном состоянии ((2 = 1), то на

Рис. 10.9. Схема//(-триггера (а), построенная на основе двухступенчатого синхронного /й'-триггера, и его условное графическое обозначение (б)

один из входов элемента 1 поступает сигнал () = 0. В этом случае на входы триггера Г, действуют сигналы 5 = К = 1, следовательно, на выходе //(-триггера сохраняется сигнал (2=1;

• комбинация / = 0, К = 1 при С = 1 соответствует режиму записи 0 (сброса). Доказывается аналогично режиму записи 1.

При комбинации J = К = 1 ]К-триггер выполняет функции Т- триггера. В этом случае /- и ЛС-входы триггера можно исключить, так как на элементы умножения &1 и &2 подаются единичные сигналы и схема //(-триггера вырождается в схему '/'-триггера.

Особенности интегральных триггеров. В интегральном исполнении находят применение три тина триггеров: /1.9-, О- и .//(-триггеры. Это обусловлено возможностями:

- • построения четвертого тина триггеров — Г-триггеров — на основе ЯЗ-, О-, //(-триггеров (рис. 10.10, а—г);

- • взаимного преобразования триггеров. 11а рис. 10.11, а —в соответственно показаны схемы преобразования КБ- и .//(-триггеров в //-триггер; ///"-триггера в .//(-триггер.

Интегральные триггеры снабжены асинхронными КЗ-входами для начальной установки триггера в требуемое состояние (рис. 10.12).

Рис. 10.10. Схемы Г-триггеров, построенные на основе ЛУ-триггера (а), О-триггеров (б, в) и //(-триггера (г).

Рис. 10.11. Схемы 1)-триггеров, построенные на основе /^-триггера (а) и //^-триггера (б); схема//^-триггера (в), построенная на основе /^-триггера.

Рис. 10.12. /^-триггер с асинхронными /?5-входами.

Асинхронные входы по отношению к другим входам триггера обладают приоритетом. Это означает, что при активизации асинхронных входов другие входы триггера блокируются и поданные на них сигналы не оказывают воздействия на триггер. Наиболее часто на асинхронные_входы подают инверсные сигналы. Комбинация сигналов 5 = 0, /? = 1 соответствует режиму записи 1 на ()-выход триггера; комбинация 5 = 1, Я = 0 — режиму записи 0. При этих комбинациях сигналов действие других входов триггера заблокировано. При 5 = 1, Я = 1 блокировка снимается, и триггер управляется по своим основным входам. Комбинация 5 = 0, Я = 0 запрещена.