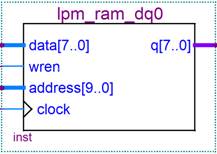

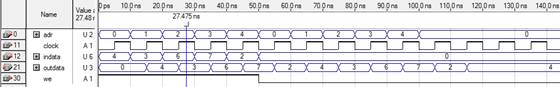

По условию задания необходимо реализовать оперативное запоминающее устройство, работающее в синхронном режиме. Данное устройство будет реализовано в виде отдельного блока, согласно данной по условию архитектуре системы. Рассмотрим работу ОЗУ и временные диаграммы его работы. Условно-графическое изображение ОЗУ приведено на рисунке 2.3, а временная диаграмма работы — на рисунке 2.4.

Рисунок 2.3 — Условно-графическое изображение ОЗУ.

Рисунок 2.4 — Временная диаграмма работы ОЗУ.

Для проверки были поданы из порта DAT произвольные данные и записаны в ОЗУ, а после считаны.

Листинг 2.2 реализация VHDL-кода ОЗУ.

USE ieee. std_logic_1164.all;

LIBRARY altera_mf;

USE altera_mf. all;

ENTITY lpm_rom0 IS.

PORT.

(.

address: IN STD_LOGIC_VECTOR (9 DOWNTO 0);

clock: IN STD_LOGIC := '1';

q: OUT STD_LOGIC_VECTOR (7 DOWNTO 0).

);

END lpm_rom0;

ARCHITECTURE SYN OF lpm_rom0 IS.

SIGNAL sub_wire0: STD_LOGIC_VECTOR (7 DOWNTO 0);

COMPONENT altsyncram.

GENERIC (.

clock_enable_input_a: STRING;

clock_enable_output_a: STRING;

init_file: STRING;

intended_device_family: STRING;

lpm_hint: STRING;

lpm_type: STRING;

numwords_a: NATURAL;

operation_mode: STRING;

outdata_aclr_a: STRING;

outdata_reg_a: STRING;

widthad_a: NATURAL;

width_a: NATURAL;

width_byteena_a: NATURAL.

);

PORT (.

clock0: IN STD_LOGIC ;

address_a: IN STD_LOGIC_VECTOR (9 DOWNTO 0);

q_a: OUT STD_LOGIC_VECTOR (7 DOWNTO 0).

);

END COMPONENT;

BEGIN.

q <= sub_wire0(7 DOWNTO 0);

altsyncram_component: altsyncram.

GENERIC MAP (.

clock_enable_input_a => «BYPASS» ,.

clock_enable_output_a => «BYPASS» ,.

init_file => «rom. mif» ,.

intended_device_family => «Stratix II» ,.

lpm_hint => «ENABLE_RUNTIME_MOD=NO» ,.

lpm_type => «altsyncram» ,.

numwords_a => 1024,.

operation_mode => «ROM» ,.

outdata_aclr_a => «NONE» ,.

outdata_reg_a => «CLOCK0» ,.

widthad_a => 10,.

width_a => 8,.

width_byteena_a => 1.

).

PORT MAP (.

clock0 => clock,.

address_a => address,.

q_a => sub_wire0.

);

END SYN;