Система команд.

Архитектура ЭВМ и систем

В наборе имеются команды, позволяющие реализовать безусловную (RET) и условную (К**) передачу управления для возврата в прерванную программу. При выполнении этих команд адрес возврата переписывается из стека в программный счетчик PC, для чего используется постинкрементный способ адресации. При невыполнении условия возврата (для команды с условием) осуществляется переход к очередной команде путем… Читать ещё >

Система команд. Архитектура ЭВМ и систем (реферат, курсовая, диплом, контрольная)

Общие сведения. Фиксированный набор команд конкретного микропроцессора называют системой команд. Функциональные способности процессора определяются совокупностью базовых команд с различными кодами операций. Общее число команд (кодов операции) в системе всегда больше числа базовых команд. Например, к базовой команде относится команда MOV dst, scr, которая обеспечивает функцию пересылки данных из источника scr в приемник dst. Таких команд в системе может быть очень много. Система команд представляется в виде таблицы. Таблица может иметь различную структуру, однако обычно она содержит следующие сведения о команде:

- • мнемоническое обозначение команды, представляющее собой сокращенную запись названия команды. Для этого используются 3−4 латинские буквы названия операции, выполняемой командой. Мнемоника является удобной формой представления кода операции команды. Также она используется при описании команды на языке ассемблера. Программа ассемблера преобразует мнемоническое обозначение кодов операции в соответствующие двоичные эквиваленты;

- • шестнадцатеричные коды команд;

- • влияние выполненной команды на флаги регистра состояния программы;

- • число байтов в команде и число машинных циклов и тактов, затрачиваемых на выполнение команды;

- • словесное и (или) символьное описание выполняемой командой операции.

Часто для удобства систему команд разбивают на отдельные группы по функциональному признаку. Например, систему команд микропроцессора КР580ВМ80, содержащую 78 базовых команд, разбивают на 5 групп [18]. Ниже приведено краткое описание функциональных особенностей команд каждой группы.

Команды имеют длину от 1 до 3 байт. Код операции всегда размещен в первом байте команды. Второй байт команды отводится под непосредственный операнд или адрес порта, второй и третий байты являются адресом ячейки памяти. Команды допускают явное задание только одного адреса памяти, т. е. относятся к классу одноадресных команд. При описании команд используются следующие обозначения:

- • src, dst — 8-разрядные источник и приемник. Источником или приемником может быть один из 8-разрядных регистров А, В, С, D, Е, Н или ячейка памяти М, доступ к которой обеспечивает регистровая пара Н L, содержащая адрес пересылаемого байта. В коде операции источник src и приемник dst указаны в виде трехразрядного кода SSS и DDD;

- • RP — двухразрядный код регистровых пар ВС, DE, Н L, А + РП (регистр признаков) или указателя стека SP;

- • data, data 16 — 8- и 16-разрядный операнд;

- • addr, port — 16-разрядный адрес памяти и 8-разрядный адрес порта;

- • (addr), (SP) — содержимое ячейки памяти по указанным адресам;

- • (SP)+, -(SP) — операции постинкремента и предекремента со стеком. Команды пересылки. Г руппа содержит наиболее часто встречающиеся в программах команды пересылки данных, источниками и приемниками которых могут быть внутренние регистры процессора, основная память и внешние устройства. Команды не оказывают воздействия на флаги регистра состояния.

Мнемоника команды отражает особенности выполняемой операции и способ адресации. Например, мнемоника MOV, MVI указывает на перемещение (Move) операндов; LDA, LDAX, LXI, LHLD — на загрузку (Load); STA, STAX, SHLD — на сохранение (Save). Для операций с байтами используется мнемоника MOV, MVI, LDA, STA, LDAX, STAX; для операций со словами- LXI, LHLD, SHLD. Прямая адресация при загрузке и сохранении содержимого аккумулятора отражается мнемоникой LDA и STA, косвенная — мнемоникой LDAX и STAX.

Команды этой группы сведены в табл. 5.8. Они позволяют осуществить:

- • операцию пересылки данных между источником (src) и приемником (dst), которая записывается в виде dst < src (команда 1). Источниками и приемниками являются внутренние регистры общего назначения (А, В, С, D, Е, Н) и ячейка памяти М. Допускается любая комбинация, за исключением М < М, т. е. перезагрузка ячейки памяти М не разрешается;

- • загрузку регистров общего назначения и ячейки М вторым байтом В2 (команда 2) и регистровых пар ВС, DE, HL (в том числе указателя стека SP) вторым В2 и третьим В3 байтами (команда 3), причем всегда В3 загружается в старшие регистры (В, D, Н) пары, В2 — в младшие регистры (С, Е, L);

- • пересылку данных между аккумулятором, А и основной памятью (команды 4?7), между аккумулятором и внешним устройством (команды 8, 9). При пересылке между аккумулятором, А и памятью адреса ячеек памяти располагаются в регистровых парах ВС, DE или в третьем и втором байтах (В3В2) команды;

Таблица 5.8

№. п/п. | Мнемоника команды. | Выполняемая операция. | Код операции. | Число. | |||

Б. | U. | T. | |||||

MOV. | dst, src. | dst < src. | OIDDDSSS. | ½. | 5/7. | ||

MVI. | dst, data. | dst < data. | 00DDDII0. | 2/3. | 5/10. | ||

LX1. | RP, data 16. | RP < data 16. | 00RP0001. | ||||

LDA. | addr. | А < (addr). | ЗА. | ||||

STA. | addr. | (addr) < A. | |||||

LDA. | RP. | A" - (RP). | 00RPI0I0. | ||||

STAX. | RP. | (RP) < A. | 00RP0010. | ||||

IN. | port. | A <- (port). | DB. | ||||

OUT. | port. | (port) < A. | D3. | ||||

LHLD. | addr. | HL < (addr). | 2A. | ||||

SHLD. | addr. | (addr) <- HL. | |||||

PUSH. | RP. | -(SP) < RP. | 11RP0101. | ||||

POP. | RP. | RP<-(SP) +. | 11RP0001. | ||||

SPHL. | SP^L. | F9. | |||||

PCHL. | PC < HL. | E9. | |||||

XCHG. | DE — HL. | EB. | |||||

XTHL. | (SP) — HL. | E3. | |||||

Примечания: RP — 2-разрядный код регистровых пар ВС, DE, HL, А + РП (регистр признаков) или указателя стека SP; Б — байты, U — циклы, Т — циклы.

- • пересылку данных между парой регистров HL и памятью (команды 10, 11). При этом операнд из регистра L пересылается в ячейку с адресом В3В2, образованным из третьего и второго байта команды, а из регистра Н — по адресу на единицу больше. При обратной пересылке сначала из ячейки с адресом В3В2 в регистр L загружается первый операнд, затем из ячейки с адресом В3В2+1 в регистр Н — второй;

- • пересылку данных между парами регистров, включая пару из аккумулятора, А и регистра признаков РП, и стеком (команды 12, 13). При записи в стек содержимое указателя стека уменьшается на единицу, и по адресу SP-1 загружается первый операнд в один из регистров В, D, Н или А, затем содержимое указателя стека снова уменьшается на единицу, и по адресу SP-2 загружается второй операнд из регистра С, Е, L или РП. При выводе из стека сначала в один из регистров С, Е, L или РП загружается операнд, хранящийся в ячейке с адресом SP указателя стека. Затем содержимое увеличивается на единицу, из ячейки с адресом SP + 1 второй операнд загружается в один из регистров В, D, Н или А, и содержимое указателя стека вновь увеличивается на единицу и принимает значение SP + 2. Следует отметить, что при загрузке регистровой пары А, РП (ее код RP = 11) из стека изменяется состояние триггеров регистра признаков РП. Это единственная команда (из всех команд пересылки данных), которая влияет на признаки;

- • пересылку содержимого пары регистров HL в указатель стека SP и программный счетчик PC (команды 14, 15);

- • обмен данными между парами регистров HL и DE, парой регистров HL и стеком (команды 16, 17). При обмене содержимое регистровой пары HL помещается в пару DE или стек, а содержимое регистровой пары DE или стека — в пару HL. Операция обмена обозначается символом «-» .

Арифметические команды. Вычислительные возможности микропроцессора ограничены простыми командами сложения и вычитания 8-разрядных операндов. Операции умножения и деления реализуются программным способом. Набор команд (табл. 5.9) позволяет выполнить:

- • сложение и вычитание 8-разрядных операндов с учетом и без учета переноса (команды l?8), при этом один из операндов всегда находится в аккумуляторе, а второй — в одном из регистров общего назначения (ячейке памяти М) или является вторым байтом команды. Команды, учитывающие значение сигнала переноса С регистра признаков, используются при сложении и вычитании многобайтных чисел. Для этой же цели можно использовать команду 9 сложения содержимого пары регистров HL с 16-разрядным адресуемым регистром;

- • арифметическое сравнение содержимого аккумулятора, А с содержимым одного из регистров общего назначения Rn (ячейкой памяти М) или вторым байтом В2 (команды 10+11). При этом выполняется вычитание, А — Rn или, А — В2. Результат сравнения определяется по сигналам триггеров регистра признаков: если Z = 1, то A = Rn или, А = В2; если S = 1, то, А > Rn или, А > В2. Содержимое аккумулятора не изменяется;

- • увеличение и уменьшение на 1 (инкремент и декремент) содержимого регистров и регистровых пар. При программировании часто

Таблица 5.9

№. п/п. | Мнемоника команды. | Выполняемая операция. | Код операции. | Число. | CVZSP. | |||

Б. | U. | T. | ||||||

ADD. | src. | А < A + src. | I0000SSS. | ½. | 4/7. | + + + + +. | ||

ADC. | src. | А < A + src + C. | 10001SSS. | ½. | 4/7. | + + + + +. | ||

SUB. | src. | A < A — src. | I0010SSS. | ½. | 4/7. | + + + + +. | ||

SBB. | src. | 1001ISSS. | ½. | 4/7. | + + + + +. | |||

ADI. | data. | C6. | + + + + +. | |||||

АСI. | data. | А < A + data + CY. | CE. | + + + + +. | ||||

SUI. | data. | A < A — data. | D6. | + + + + +. | ||||

SBI. | data. | А < A — data — CY. | DE. | + + + + +. | ||||

DAD. | RP. | HL< HL + RP. | 00RPI00I. | + ; | ||||

CMP. | src. | A — scr (сравнение). | 1011ISSS. | ½. | 4/7. | + + + + +. | ||

CPI. | data. | A — scr (сравнение). | FE. | ½. | 4/7. | + + + + +. | ||

INR. | dst. | dst < dst +1. | 00DDD100. | 1/3. | 5/10. | — + + + +. | ||

DCR. | dst. | dst < dst — 1. | 00DDD101. | 1/3. | 5/10. | — + + + +. | ||

INX. | RP. | DE < RP + 1. | 00RP0011. | |||||

DCX. | RP. | BC< RP — I. | 00RP1011. | |||||

DAA. | A < 2/10-коррекция A. | + + + + +. | ||||||

возникает необходимость увеличения или уменьшения на единицу значения операнда. Для этого можно использовать операции сложения, А + В2 или вычитания, А — В2, записав в программе В2 = 1. Однако в системе команд предусмотрены специальные команды (12−5-15) инкремента и декремента 8- и 16-разрядных операндов;

• десятичную коррекцию содержимого аккумулятора после выполнения арифметических операций в двоично-десятичном коде 8421 (команда 16). При этом содержимое аккумулятора представляется в виде двух полубайтов, каждый из которых соответствует десятичной цифре. Коррекция производится блоком десятичной коррекции по изложенным в § 5.2 правилам (с. 99).

Команды логических операций. Команды этой группы (табл. 5.10) позволяют реализовать:

- • двуместные логические операции умножения (И), сложения (ИЛИ) и исключающее ИЛИ над 8-разрядными операндами (команды 1?6). Логические операции являются поразрядными и выполняются независимо для каждого из восьми бит операндов. Неадресуемый операнд находится в аккумуляторе, туда же поступает результат операции. Вторым операндом является содержимое одного из регистров общего назначения (ячейки памяти М) или второй байт команды;

- • инвертирование содержимого аккумулятора, А (команда 7);

- • флаговые команды (8, 9) инвертирования и установки бита С триггера переноса регистра признаков;

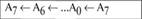

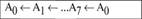

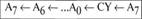

- • два вида циклических сдвигов содержимого аккумулятора влево и вправо (команды Юл-13). Первый вид сдвигов (сдвиги без переноса) реализуется путем замыкания в кольцо всех триггеров аккумулятора, при втором виде сдвигов (сдвиги с переносом, или расширенные сдвиги) в кольцо дополнительно вводится триггер переноса С регистра признаков. Отсутствующие в системе команд логические и арифметические сдвиги в обе стороны можно реализовать предварительной установкой бита С в 0 или 1 совместно с расширенным сдвигом.

Команды передачи управления. При передаче управления нарушается последовательный ход выборки содержимого ячеек памяти и процессор адресуется в другую область памяти. Выделяют.

Таблица 5.10

№. п/п. | Мнемоника команды. | Выполняемая операция. | Код операции. | Число. | CVZSP. | |||

Б. | U. | T. | ||||||

ANA. | src. | А < А л src — умножение. | 10100SSS. | l. | ½. | 4/7. | 00 + + +. | |

ORA. | src. | А < A v src — сложение. | 10II0SSS. | ½. | 4/7. | 00 + + +. | ||

XRA. | src. | А < A © src — искл. ИЛ И. | 10I01SSS. | ½. | 4/7. | 00 + + +. | ||

ANI. | data. | А < А л data. | E6. | 00 + + +. | ||||

ORI. | data. | А < A v data. | F6. | 00 + + +. | ||||

XRI. | data. | А < A © data. | EE. | 00 + + +. | ||||

CMA. | А < A. | 2E. | ||||||

CMC. | C. | 3 °F. | + ; | |||||

STC. | C< 1. | + ; | ||||||

RLC. |  | + ; | ||||||

RRC. |  | OF. | ||||||

RAL. |  | |||||||

RAR. |  | IF. | + ; | |||||

три вида команд передачи управления: команды перехода по заданному адресу (JMP), вызова подпрограммы (CALL) и возврата из подпрограммы (RET). К ним относятся безусловные и условные команды. Условные команды осуществляют переход, вызов подпрограммы и возврат из подпрограммы в зависимости от состояния флага, задаваемого значением сигнала одного из четырех триггеров Z, С, S, Р регистра признаков (или состояния). В процессоре 8080 используются оба состояния (1 и 0) четырех флагов (Z, С, Р, S), позволяющих получить 8 вариантов каждой команды (табл. 5.11). Обозначение признака (условия) указывается в мнемонике условных команд J**, С**, R** вместо звездочек (**). Например, признаку NC, для которого условия перехода считаются выполненными при С = 0, соответствует команда JNC.

В операциях как условного, так и безусловного перехода и вызова подпрограмм используется полный прямой 16-разрядный адрес, обеспечивающий передачу управления в любую точку 64-килобайтовой области пространства памяти.

Таблица 5.11

Обозначение условия (**). | Код условия (XXX). | Значение бита при выполнении условия. | Обозначение условия (**). | Код условия (XXX). | Значение бита при выполнении условия. |

NZ. | z = o. | Z. | 00 1. | Z = 1. | |

NC. | 0 1 0. | С = 0. | С. | 0 1 1. | С = 1. |

РО. | Р = 0. | РЕ. | р= 1. | ||

Р. | 1 1 0. | S = 0. | М. | 1 1 1. | S = 1. |

Рассмотрим особенности команд, представленных в табл. 5.12.

С помощью трехбайтной команды JМР реализуется безусловная передача управления. При этом второй и третий байты команды (адрес addr продолжения программы) заносятся в счетчик команд PC (содержимое В3 в старшие разряды, В2 — в младшие).

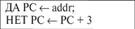

Команды условной передачи управления J** реализуют разветвление вычислительного процесса в зависимости от условия. При выполнении условия (ДА) в счетчик PC заносится второй и третий байты команды, в противном случае (НЕТ) содержимое счетчика увеличивается на 3 единицы. Продолжение программы осуществляется по адресу, находящемуся в счетчике команд, т. е. со следующей команды.

Таблица 5.12

№. п/п. | Мнемоника команды. | Выполняемая операция. | Код операции. | Число. | ||

Б. | LI. | T. | ||||

JMP add г. |  | сз. | ||||

J** addr. |  | 11XXX0I0. | ||||

CALL addr. |  | |||||

С** addr. |  | 11XXXI00. | 5/3. | 17/11. | ||

RET. |  | CD. | II. | |||

R**. |  | I1XXX000. | 3/1. | 11/5. | ||

PCHL. |  | E9. | ||||

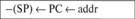

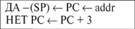

Команды безусловного (CALL) и условного (С**) вызовов используются для обращения к подпрограммам, хранящимся в другой части основной памяти. Эти команды всегда предусматривают возможность возврата в прерванную основную программу путем сохранения в стеке содержимого программного счетчика PC. После выполнения операции возврата:

- • при безусловном вызове или выполнении условия второй и третий байты команды заносятся в программный счетчик PC;

- • при невыполнении условия содержимое программного счетчика увеличивается на 3 единицы.

Продолжение программы осуществляется по адресу, находящемуся в счетчике команд PC.

В наборе имеются команды, позволяющие реализовать безусловную (RET) и условную (К**) передачу управления для возврата в прерванную программу. При выполнении этих команд адрес возврата переписывается из стека в программный счетчик PC, для чего используется постинкрементный способ адресации. При невыполнении условия возврата (для команды с условием) осуществляется переход к очередной команде путем увеличения на единицу содержимого программного счетчика PC. Команды возврата являются однобайтными, так как в указателе стека SP хранится адрес ячейки стека с адресом возврата в прерванную программу.

Команда PCHL загружает в программный счетчик PC адрес, хранящийся в регистровой паре HL.

Команды общего управления. Команды этой группы (табл. 5.13) используются для задания режима работы микропроцессора. Команда RST применяется для повторного пуска микропроцессора и при обслуживании прерываний. При ее выполнении:

- • содержимое программного счетчика переносится в стек по адресам SP — 1, SP — 2, формируемым в указателе стека, что обеспечивает возврат к основной программе;

- • в программный счетчик засылается 16-разрядный адрес начала одной из 8 программ обслуживания прерывания.

Таблица 5.13

№. п/п. | Мнемоника команды. | Выполняемая операция. | Код операции. | Число. | ||

Б. | U. | Т. | ||||

RST п. | -(SP) < PC < 8? n, n = 0 — 7. | 11NNN111. | ||||

EI. | Разрешение прерываний. | FB. | ||||

DI. | Запрет прерываний. | F3. | ||||

RIM. | Чтение маски. | ; | ||||

SIM. | Установка маски. | |||||

HLT. | Останов. | |||||

NOP. | Нет операции. | |||||

Команда разрешения прерывания EI устанавливает триггер INTE разрешения прерываний в единичное состояние, при этом микропроцессор реагирует на запросы прерываний. Команда запрещения прерываний DI устанавливает триггер INTE в нулевое состояние. Пустая команда NOP используется в циклах программируемой задержки. Команда останова HLT вызывает прекращение выполнения программы.