Другие работы

Модель потребления информации в сети Интернет управляется аудиторией, но не поставщиком информации. Это и есть нелинейное потребление. Такая модель потребления информации вызывает потребность заново продумать процесс написания текстов. Если вместо этого продолжать представлять информацию отдельными гомогенными единицами, как это сделали бы журналисты в газете, читатель прочтет только один…

Реферат

Главная форма приложения MainClientsForm, также содержит компоненты, обеспечивающие взаимодействие приложения с базой данной, реализованной в СУБД MS Access: компонент AdoConnection, компонент DataSource, 2 компонента AdoQuery, 5 компонентов AdoTable1, соответствующих каждой из таблиц базы данных Главное меню приложения содержит альтернативы «файл», «Справочники», «создать», «Найти». Альтернатива…

Курсовая

Получение ответов от web-ссрвсров и их интерпретация для создания визуального представления для пользователя. В самом простом случае ото требует проверки некоторых заголовков ответа, таких как Content-Type, для определения того, какие действия требуется выполнить и какой способ визуализации (рэндеринга) требуется; Формирование и передача запросов web-серверам от имени пользователей в результате…

Реферат

Системы искусственного интеллекта — реализуют отдельные функции интеллекта человека. К ним относятся экспертные системы, системы анализа и распознавания речи, образов. Диагностика — выявление причин неисправного функционирования системы по результатам наблюдений. Проектирование — построение конфигурации объектов при заданных ограничениях. Наблюдение — сравнение результатов наблюдения с ожидаемыми…

Реферат

Справочники содержат значения измерений, т. е. качественную информацию, характеризующую факты. Типичными измерениями процесса продаж являются товары (что продано), покупатели (кому продано), каналы сбыта (кем продано), средства продвижения (с помощью каких мероприятий по продвижению осуществлена продажа). Необходимым измерением любого хранилища является время (дата). Каждый справочник содержит…

Реферат

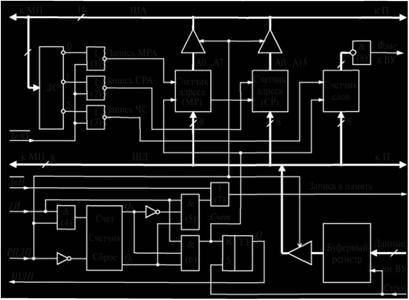

Диспетчер кэша, повышающий производительность файлового ввода-вывода за счет сохранения в основной памяти дисковых данных, к которым недавно было обращение (это также уменьшает число обращений к диску для записи, поскольку модифицированные данные предварительно накапливаются в памяти в течение определенного периода). Как видите, диспетчер кэша выполняет эту задачу, используя поддержку…

Реферат

Теоретически при осуществлении этого выбора нужно принимать во внимание десятки факторов. Но на практике разработчики руководствуются лишь собственной интуицией и несколькими наиболее важными критериями, к которым, в частности, относятся: Х и 64-х разрядные версии Windows, Linux, также MacOS X, HP-UX, FreeBSD, Solaris и др. Наиболее широко используемыми для серверов «Firebird» операционными…

Реферат

С точки зрения потребителя эти характеристики позволяют получить услуги с высоким уровнем доступности (англ. high availability) и низкими рисками неработоспособности, обеспечить быстрое масштабирование вычислительной системы благодаря эластичности без необходимости создания, обслуживания и модернизации собственной аппаратной инфраструктуры. Учет потребления, когда поставщик услуг автоматически…

Реферат

Важно ещё отметить, что факультативные занятия должны быть интересными, увлекательными. Хорошо известно, что занимательность изложения помогает раскрытию содержания сложных научных понятий и проблем. Занимательность поможет школьникам освоить факультативный курс, содержащиеся в нём идеи и методы математической науки, логику и приёмы творческой деятельности. В этом отношении цель учителя…

Реферат

Системы подготовки презентаций предназначены для квалифицированной подготовки графических и текстовых материалов, используемых в целях демонстрации на презентациях, деловых переговорах, конференциях. Для современных технологий подготовки презентаций характерно дополнение традиционных графики и текста такими формами информации, как видеои аудиоинформация, что позволяет говорить о реализации…

Реферат

Около 20 лет назад Министерство Обороны США создало сеть, — она называлась ARPAnet. ARPAnet была экспериментальной сетью, — она создавалась для поддержки научных исследований в военно-промышленной сфере, — в частности, для исследования методов построения сетей, устойчивых к частичным повреждениям, получаемым, например, при бомбардировке авиацией и способных в таких условиях продолжать нормальное…

Реферат

Сеть абонентского доступа — это совокупность технических средств между оконечными абонентскими устройствами, установленными в помещении пользователя, и тем коммутационным оборудованием, в план нумерации (или адресации) которого входят подключаемые к телекоммуникационной системе терминалы. Исходя из данного определения, границы сети абонентского доступа достаточно широко варьируются в зависимости…

Реферат

База программный автомобиль целостность Описание таблицы «клиент». Выводить информацию об имеющихся автомобилях по любому запросу. Таблица 2 «клиент» содержит информацию обо всех клиентах. Поле «код машины» является ключевым. Схема данных приведена на рисунке 1. Описание структуры таблицы «авто». Поле «Код» является ключевым. Вводить данные по заявке. Формат # ##0″ р." ;-# ##0″ р.". Формат…

Реферат

Основные непреднамеренные искусственные угрозы АС (действия, совершаемые людьми случайно, по незнанию, невнимательности или халатности, из любопытства, но без злого умысла): Разглашение, передача или утрата атрибутов разграничения доступа (паролей, ключей шифрования, идентификационных карточек, пропусков и т. п.); Вход в систему в обход средств защиты (загрузка посторонней операционной системы…

Реферат

Преподаватели различных образовательных организаций изучали, как применяются цифровые ресурсы в обучении. А. Ш. Аипова исследовала цифровые образовательные ресурсы и адаптивное обучение. Л. В. Буйлова применяла цифровые образовательные ресурсы в обучении студентов техническим дисциплинам. О. П. Осипова и З. С. Ишмуратова использовали цифровые образовательные ресурсы в обучении младших школьников…

Реферат