Адресация к элементам памяти

Оценим выигрыш, получаемый от использования двухкоординатной адресации для ОЗУ емкостью 1024 бита. В этом случае адресный код содержит 10 разрядов. При однокоординатной адресации дешифратор должен иметь 10 входов и 1024 выхода. Если же использовать двухкоординатную адресацию с разбивкой адресного кода на 2 слова по 5 разрядов в каждом, то дешифраторы строк и столбцов будут иметь по 5 входов… Читать ещё >

Адресация к элементам памяти (реферат, курсовая, диплом, контрольная)

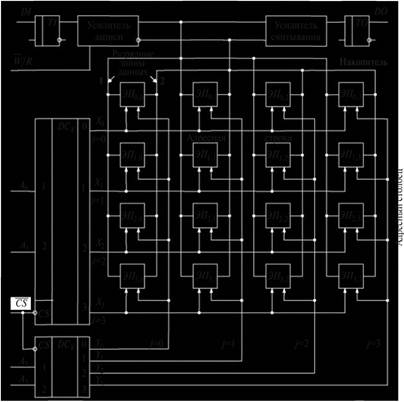

Схема статического ОЗУ, иллюстрирующая принцип двухкоординатной адресации к элементам памяти, приведена на рис. 9.3.

Состав ОЗУ. Запоминающее устройство содержит:

- • накопитель в виде матрицы из 4 строк и 4 столбцов, предназначенных для адресации к элементам памяти ЭПц (/ =0, 1, 2, 3; j = 0, 1,2, 3). Элементами памяти служат бистабильные ячейки, информационные входы-выходы которых подключены к линиям 1 и 2 разрядных шин данных;

- • дешифраторы строк DCX и столбцов DC у,

- • усилители записи и считывания;

- • два буферных триггера, включенных на входе и выходе информационного тракта ОЗУ.

Особенности работы ОЗУ. Адресный код при двухкоординатной адресации разбивается на две части. Обычно младшие разряды.

Рис. 9.3. Структурно-функциональная организация ОЗУ с двухкоординатной адресацией к элементам памяти кода подаются на входы дешифратора строк DCX, а старшие — на входы дешифратора столбцов DC у. При поступлении сигнала выбора микросхемы CS# = 0 и адресного кода на/'-й строке и j-м столбце устанавливается высокий уровень напряжения. В результате активизируется элемент памяти Э/Tjj, расположенный на пересечении /-Й строки и/-го столбца.

Если сигнал запись/считывание W#IR = 0, то усилитель записи активизирован и сего выходов на линии I и 2 разрядной шины поступает бит входных данных в прямой DI и инверсной DI# форме. Происходит запись бита в элемент памяти ЭПц.

Если сигнал W#/R = 1, то запоминающее устройство работает в режиме чтения. При этом усилитель записи переходит в Z-состояние с высоким выходным сопротивлением и не влияет на работу запоминающего устройства. В режиме чтения бит данных, хранящийся в элементе памяти, через усилитель считывания поступает на триггер и фиксируется на его выходе DO.

Оценим выигрыш, получаемый от использования двухкоординатной адресации для ОЗУ емкостью 1024 бита. В этом случае адресный код содержит 10 разрядов. При однокоординатной адресации дешифратор должен иметь 10 входов и 1024 выхода. Если же использовать двухкоординатную адресацию с разбивкой адресного кода на 2 слова по 5 разрядов в каждом, то дешифраторы строк и столбцов будут иметь по 5 входов и по 32 выхода. Такое техническое решение реализуется значительно проще.

Для иллюстрации конкретной реализации принципа адресации к элементам памяти рассмотрим микросхему К561РУ2, изготовленную по КМОП-технологии.

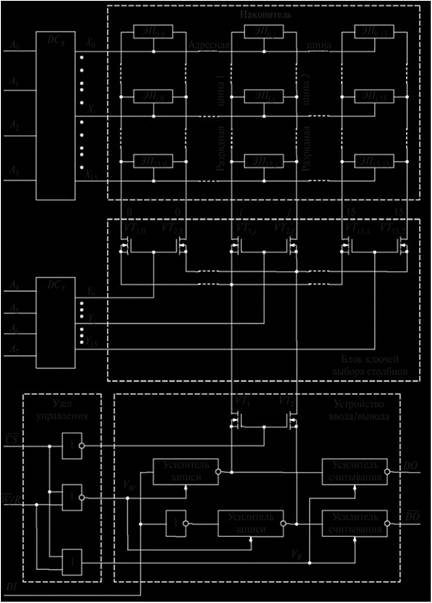

Структура СОЗУ. В состав ЗУ входят (рис. 9.4):

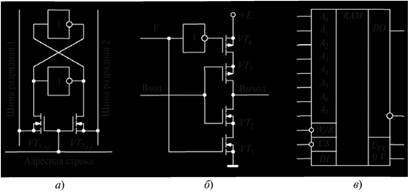

- • накопитель в виде матрицы из элементов памяти ЭПц, расположенных вдоль строк (/ =0, …, 15) и столбцов (/' =0,…, 15). Элементом памяти является бистабильная ячейка (триггер), выполненная на двух инверторах (рис. 9.5, а). Транзисторы УТуп, УТ2^ предназначен ы для подключения ячейки к разрядным шинам 1 и 2у-го столбца. Общее число элементов памяти определяет информационную емкость СОЗУ, которая равна произведению числа элементов в строке (16) на число элементов в столбце (16) и составляет 256 бит;

- • дешифраторы строк DCX и столбцов DC у, обеспечивающие выбор требуемого элемента памяти. На их входы поступает 8-разрядный адресный код А, причем на входы DCX — 4 младших разряда кода, на входы DCy- 4 старших разряда;

- • блок ключей выбора столбцов на транзисторах VT j, VTjj, отпирающихся по выходному сигналу Yj= 1 дешифратора DCy,

- • устройство ввода-вывода, содержащее усилители записи и считывания, инвертор — для получения парафазных сигналов при записи и два транзистора, УТ и УТ2, для подключения к разрядным шинам накопителя. В качестве усилителей (рис. 9.5,6) используются управляемый инвертор на транзисторах VT2, УТ2, обеспечивающий при V = 0 высокоомный выход (состояние Z) с помощью транзисторов УТ, УТ4 и логического элемента НЕ. При У= 1 транзисторы УТ{, УТ4 открыты и инвертор работает в обычном режиме;

- • узел управления, состоящий из логических элементов.

Микросхема СОЗУ имеет адресные входы А(), …, Ау, информационные вход DI и выходы DO, DO# (прямой и инверсный), вход выбора

Рис. 9.4. Структура микросхемы K56IРУ2.

микросхемы (кристалла) CS#, вход разрешения записи Wir/R (или записи/чтения) и выводы для подачи питающего напряжения. Условное графическое обозначение микросхемы приведено на рис. 9.5,в.

Рис. 9.5. Схема элемента памяти (а) и усилителя записи/считывания (б); условное графическое обозначение микросхемы К561РУ2 (в) Принцип работы. Режимы работы СОЗУ устанавливаются путем подачи сигналов на выводы микросхемы согласно табл. 9.1. При записи вначале подают код адреса А, данные D и сигнал записи W#/R = 0. Сигнал выбора микросхемы CS# = 0 устанавливается с задержкой относительно А на время tsu (A-CS) — Сохранение адреса А после подачи сигнала CS# = 1 лимитируется временем ty (cs_A). При считывании последовательность подачи управляющих сигналов сохраняется, однако W#/ R = 1. Время появления данных на выходе DO определяется временем выбора микросхемы tcs.

При поступлении адресного кода на /-м и у-м выходе дешифраторов появляются сигналы X/ = Уу? = 1 (на остальных выходах сигналы равны нулю). Сигналом Xt = 1 открываются транзисторы VTjj, ^2,ip

Таблица 9.1

CS#. | W#/R. | А. | DI. | DO. | Режим. |

Ф. | Ф. | Ф. | Z. | Хранение. | |

А. | Z. | Запись единицы. | |||

А. | Z. | Запись нуля. | |||

А. | Ф. | D. | Считывание. |

и триггеры всех ЭП^ /-й строки (т.е. для всех столбцов j = 0, 1,…, 15) подключаются к разрядным шинам 1 и 2. Однако сигнал Yj = 1 отпирает в блоке выборки столбцов лишь два транзистора — VTj и VT2j. Поэтому с поступлением сигнала выбора микросхемы CS# = 0 откроются транзисторы VT]f VT2 и к устройству ввода-вывода окажется подключенной только бистабильная ячейка элемента памяти ЭЩи расположенного на пересечении /-й строки и j-го столбца.

При записи информации (W#/R = 0) усилители записи открыты, с их выходов на разрядные шины 1-го и 2у-го столбца поступает прямое и инверсное значение входных данных DI. Если DI = 1, то в элемент памяти 3fljj записывается 1, при этом на разрядную шину 2 подается уровень логической единицы, на разрядную шину 1 — уровень логического нуля. При подаче на вход DI = 0 на разрядных шинах уровни изменяются на противоположные и в триггер запишется 0.

При считывании информации (W#/R = 1) усилители считывания открыты. Если триггер хранил 1, то с разрядной шины 1 на вход верхнего усилителя считывания поступает сигнал с нулевым логическим уровнем. Так как усилитель считывания инвертирует сигнал, с его выхода снимается сигнал в прямой форме DO =1. С нижнего усилителя снимается сигнал в инверсной форме Z)0# = 0. Если же триггер хранил 0, то сигналы на выходах микросхемы имеют противоположные значения.