Структурно-функциональная организация ПЗУ с однокоординатной адресацией

Оценим выигрыш, получаемый от использования двухадресной адресации для ОЗУ емкостью 1024 бита. В этом случае адресный код содержит 10 разрядов. При однокоординатной адресации дешифратор должен иметь 10 входов и 1024 выхода. Если же использовать двухкоординатную адресацию с разбивкой адресного кода на два слова по пять разрядов в каждом, то дешифраторы строк и столбцов будут иметь по 5 входов и 32… Читать ещё >

Структурно-функциональная организация ПЗУ с однокоординатной адресацией (реферат, курсовая, диплом, контрольная)

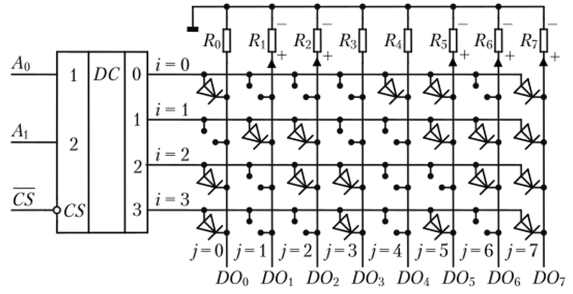

Структурные и функциональные особенности постоянного запоминающего устройства рассмотрим на примере устройства с организацией 4×11 (рис. 11.3).

Рис. 113. Структурно-функциональная организация ПЗУ с однокоординатной адресацией

Состав ПЗУ. Постоянное запоминающее устройство содержит:

- • матрицу 4×11, в которой функции элементов памяти выполняют элементы односторонней связи между строками и столбцами или отсутствие таковой. Так же как и в ОЗУ, строки служат для адресации и позволяют произвести выборку требуемого слова. Столбцы играют роль разрядных линий данных или линий считывания. Элементами связи могут быть диоды, как в рассматриваемом случае, или другие полупроводниковые приборы. Включенный между г-й строкой иу-м столбцом (г = 0, 1,2, 3 — номера строк, у = 0, 1,2,…, 7 — номера столбцов или разрядов хранимого слова) полупроводниковый диод позволяет при определенных условиях создать одностороннюю электрическую связь между ними. При отсутствии диода между г-й строкой и у-м столбцом таковой связи никогда нет. Наличие связи кодируется логической единицей, отсутствие связи — логическим нулем (или наоборот);

- • дешифратор ОС (2×4) адресного кода Л, Л0, предназначенный для активизации одной из адресных шип (строк г = 0, 1, 2, 3) с помощью сигнала С5 = 0. Для этой же цели используются сигналы с другими названиями, например «чтение памяти»;

- • резисторы Дй — Д7, предназначенные для фиксации логических уровней. Их функции могут выполнять входные сопротивления усилителей считывания, подключенных к столбцам матрицы.

Принцип работы ПЗУ. Напомним, что основными режимами работы ПЗУ являются режим хранения и режим считывания.

Если сигнал выбора микросхемы С5 = 1, то на всех выходах дешифратора формируются нулевые сигналы, через резисторы Д0 — Н7 токи не протекают и нулевые сигналы устанавливаются на всех выходах ПЗУ. Такое состояние ПЗУ соответствует режиму хранения.

Режим считывания активизируется путем подачи на входы дешифратора ОС адресного кода, например Л, Л0 = 01, и сигнала С5 = 0. При этом на выходе 1 дешифратора формируется высокий уровень напряжения (логическая единица). Через все диоды, подключенные к строке г = 1, начнет протекать ток, создавая падение напряжения на резисторах Д7, /?(;, /?., Я2, Я] (см. рис. 11.3). Из-за отсутствия связей между строкой г = 1 и столбцами у = 4, 3, 0 токи через резисторы /?, П0 не протекают, и падение напряжения на этих резисторах равно нулю. В результате на выходе запоминающего устройства формируется 11-разрядное слово [)0−0()(00~00,00., 0б.>00100п - 11 1001 10.

Еще раз подчеркнем необходимость использования элементов с односторонней проводимостью для организации связи между г-й строкой и у-м столбцом, благодаря которым под напряжением находится только активная строка. Если вместо полупроводниковых диодов включить обычные перемычки с двухсторонней проводимостью, то под напряжением могут оказаться все строки и запоминающее устройство не будет выполнять свои функции.

Недостаток однокоординатной адресации состоит в том, что с увеличением емкости памяти М х N. или числа хранимых слов М (так как обычно М Л'), растет число выходов дешифратора, что приводит к усложнению его схемы.

Рассмотрим два пути устранения этого недостатка: использование двухкоординатной адресации и каскадирование запоминающих устройств.

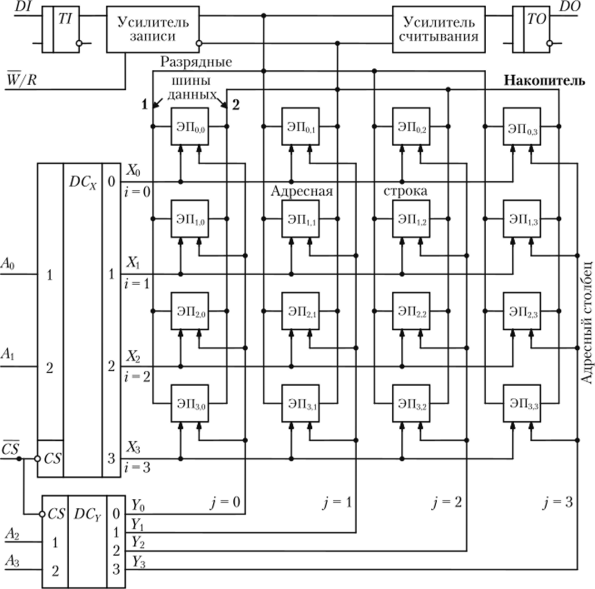

Структурно-функциональная организация статических ОЗУ с двухкоординатной адресацией. Двухкоординатная адресация позволяет упростить дешифрацию адреса при организации обращения к отдельным элементам и ячейкам памяти, так как позволяет построить накопитель с квадратной матрицей.

Двухкоординатная адресация к элементам памяти. На рис. 11.4 приведена схема ЗУ, иллюстрирующая принцип двухкоординатной адресации к ЭП.

Рис. 11.4. Структурно-функциональная организация статического ОЗУ с двухкоординатной адресацией к ЭП.

Запоминающее устройство содержит:

- • накопитель в виде матрицы из четырех строк и четырех столбцов, предназначенных для адресации к элементам памяти ЭП^(г, у = = 0, 1,2, 3). Элементами памяти служат бистабильные ячейки, информационные входы/выходы которых подключены к линиям 1 и 2 разрядных шин данных;

- • дешифраторы строк ОСх и столбцов ПСу,

- • усилители записи и считывания;

- • два буферных триггера, включенных на входе и выходе информационного тракта ОЗУ.

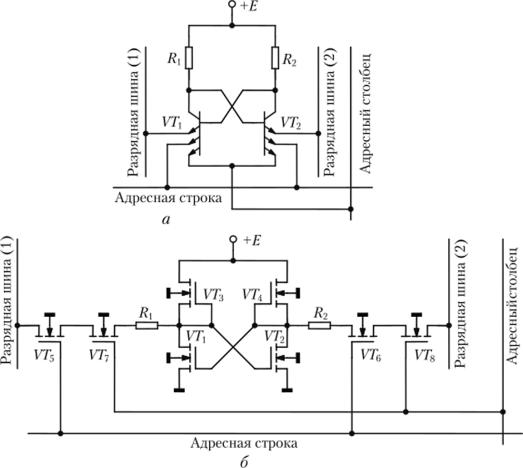

Отличие процессов, протекающих в ОЗУ в режимах записи, чтения и хранения, обусловлены несущественными особенностями схемной реализации ЭП с двухкоординатной адресацией. Принципиальные электрические схемы элементов памяти изображены на рис. 11.5. При построении элементов памяти на основе биполярной транзисторной логики используются трехэмиттерные транзисторы (рис. 11.5, а). Верхние эмиттеры транзисторов подключаются к разрядным шинам, средние эмиттеры — к адресной строке и нижние эмиттеры — к адресному столбцу. Отличие ЭП с двухкоординатной адресацией на я-МОП-транзисторах (рис. 11.5, б) по отношению к элементу с однокоординатной адресацией состоит в том, что.

Рис. 11.5. Принципиальные электрические схемы ЭП на биполярных (а) и МОП-гранзисторах (б) для двухкоординатной адресации в цепь подключения ЭГ1 к разрядной шине введены дополнительные транзисторы УГ7, УТп. Затворы этих транзисторов соединены со столбцами матричного накопителя.

Адресный код при двухкоординатной адресации разбивается на две части. Обычно младшие разряды кода подаются на входы дешифратора строк ?)СХ, а старшие — на входы дешифратора столбцов ЪСу. При поступлении сигнала выбора микросхемы С5 = О и адресного кода, расположенного в г-й строке и у-м столбце, устанавливается высокий уровень напряжения. В результате активизируется элемент памяти ЭП,-, расположенный на пересечении г-й строки иу-го столбца.

Если сигнал запись/считывание ?/Я = 0, то усилитель записи активизирован и с его выходов на линии 1 и 2 разрядной шины поступает бит входных данных в прямой П1 и инверсной П1 форме. Происходит запись бита в элемент памяти ЭП~.

Если сигнал IV/К = 1, то запоминающее устройство работает в режиме чтения. При этом усилитель записи переходит в 7-состояние с высоким выходным сопротивлением и не влияет на работу ЗУ. В режиме чтения бит данных, хранящийся в элементе памяти, через усилитель считывания поступает на триггер и фиксируется на его выходе? Ю.

Оценим выигрыш, получаемый от использования двухадресной адресации для ОЗУ емкостью 1024 бита. В этом случае адресный код содержит 10 разрядов. При однокоординатной адресации дешифратор должен иметь 10 входов и 1024 выхода. Если же использовать двухкоординатную адресацию с разбивкой адресного кода на два слова по пять разрядов в каждом, то дешифраторы строк и столбцов будут иметь по 5 входов и 32 выхода. Такое техническое решение реализуется значительно проще.

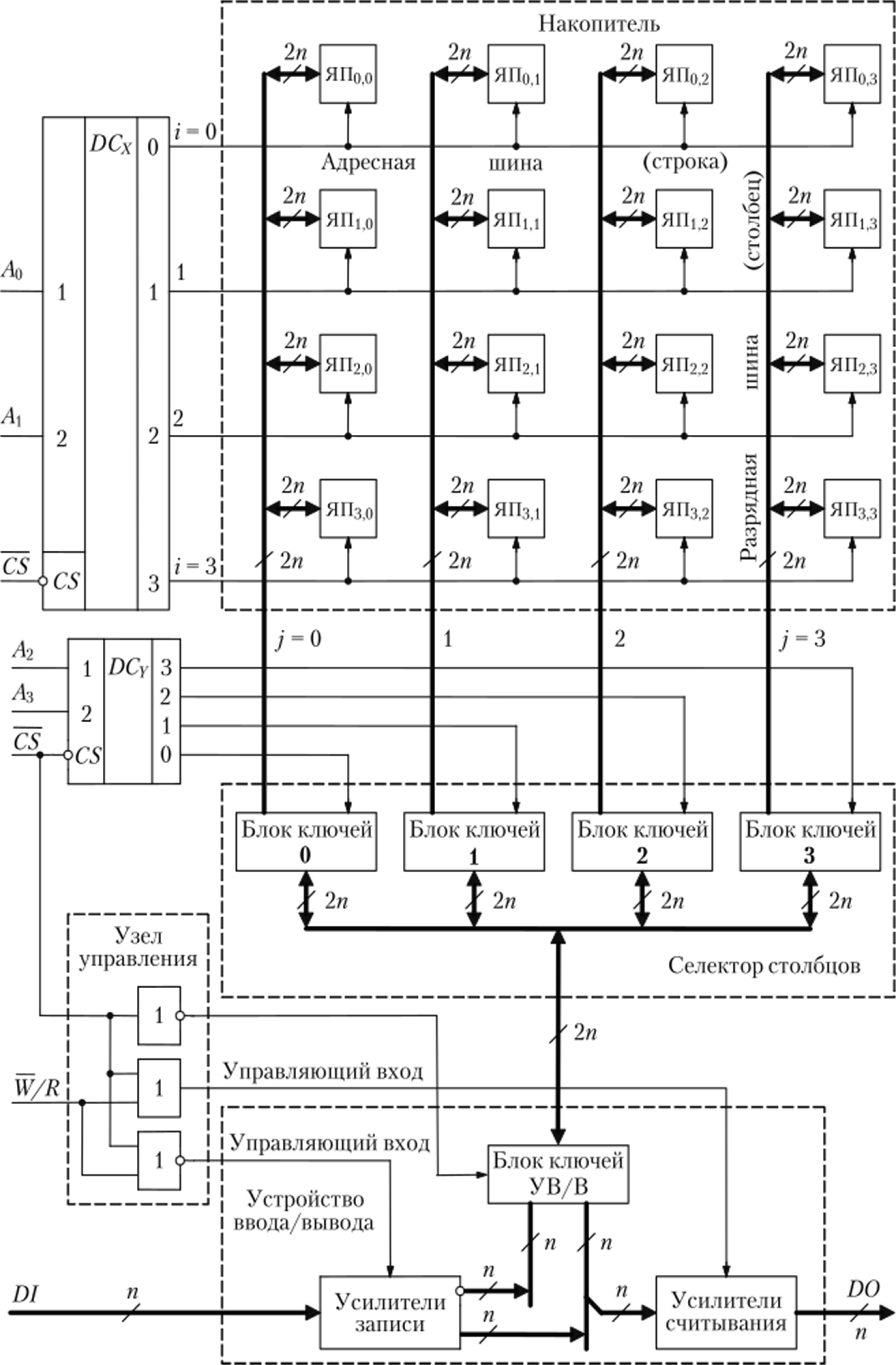

Двухкоординатная адресация к ячейкам памяти. На рис. 11.6 приведена схема статического ОЗУ, иллюстрирующая принцип двухкоординатной адресации к ЯП.

Запоминающее устройство содержит:

- • накопитель, составленный из 16 ячеек памяти в виде матрицы 4×4. Каждая ЯП предназначена для хранения «-разрядного слова. Предполагается, что ЭП выполнены на МОП-транзисгорах, но схеме, изображенной на рис. 11.2, б. Управляющие выходы ЭП (затворы МОП-транзисторов) соединены с адресной строкой, а два информационных выхода подключены к разрядным линиям, образующим 2"-разрядную шину для каждой ячейки. На рис. 11.6 шины обозначаются толстой чертой с указанием числа линий в шине;

- • два дешифратора 2×4 (ОСх — строк, ОСу — столбцов);

- • устройство ввода/вывода (УВВ), состоящее из усилителей записи и считывания, а также блоков ключей УВВ на МОП-транзисторах, используемому для поделючения УВВ к селектору столб-

Рис. 11.6. Структура статического ОЗУ с двухкоординатной адресацией к ЯП цов. Активному состоянию усилителей соответствует единичный сигнал на управляющем входе. Предполагается, что при подаче нулевого сигнала на управляющий вход усилители переводятся в высокоомное 7-состояние. Каждый усилитель записи имеет прямой и инверсный выходы. Входы усилителей считывания подключены к я-разрядной шине, по которой передается хранимое слово в прямом коде;

- • селектор столбцов, состоящий из четырех идентичных блоков ключей на МОП-транзисторах. Общее число ключей в каждом блоке равно 2п, т. е. числу подводимых к блоку линий. Блоки ключей 0, 1, 2, 3 управляются выходными сигналами дешифратора столбцов ОСу, позволяющими подключить одну из четырех ячеек памяти у-го столбца к УВВ. Подключение осуществляется через блок ключей УВВ, управляемый сигналом выбора микросхемы С5;

- • узел управления, предназначенный для управления вводом/выводом информации (режимами работы ОЗУ).

Рассмотрим работу ОЗУ в режимах записи, чтения и хранения. В режимах записи и чтения на входы ОЗУ выставляются адресный код А3Ау41А0 и сигнал выбора микросхемы С5 = 0. При этом с помощью дешифраторов 7) СЛ, /)СУ активизируются одна из адресных строк и блок ключей, обслуживающий один из столбцов. В дальнейшем будем полагать, что активными являются строка / = 2 и столбец7=1. При выбранных условиях к устройству ввода/вывода подключается ячейка памяти, расположенная на пересечении 2-й строки и 1-го столбца, т. е. ЯП2 ,.

При сигнале запись/считывание ?/Я = 0 реализуется режим записи, так как активными являются усилители записи, на управляющие входы которых подается единичный сигнал. Снимаемые с прямых и инверсных выходов усилителей разряды входного слова Д/ поступают на элементы памяти ячейки ЯП9, и изменяют ее состояние в соответствии с поступившими данными.

При сигнале запись/считывание Н7/К = 1 реализуется режим чтения, так как активными являются усилители считывания, на управляющие входы которых подается единичный сигнал. Усилители записи переводятся в высокоомное состояние и не влияют на протекающие процессы.

Таким образом, запись и считывание я-разрядных слов в ОЗУ отличаются от рассмотренных выше операций записи и считывания битов только тем, что используется п каналов вместо одного.