Сравнительный анализ возможных вариантов реализации узла

Счетчик тактов реализован на 24разрядномсдвигающемрегистре. На первом такте в первый разряд регистра записывается единица, которая с выхода регистра поступает на управляющий автомат, который на следующих тактах будет записывать в первый разряд регистра ноль, сдвигая тем самым единицу в старший разряд. Появление единицы в 22разрядесигнализирует о том, что цикл закончен. На рисунке 2представлена… Читать ещё >

Сравнительный анализ возможных вариантов реализации узла (реферат, курсовая, диплом, контрольная)

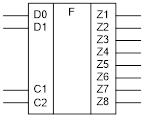

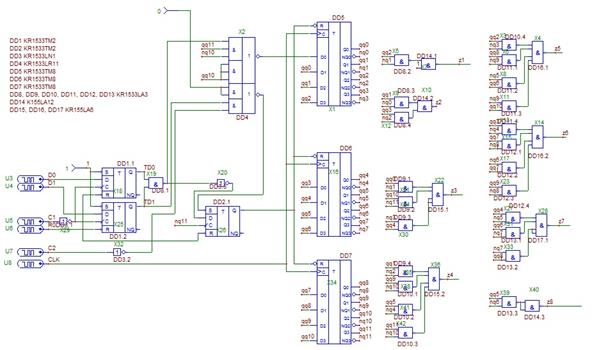

Данная разрабатываемая схема представляет собой специализированный распределитель импульсов (Рисунок 1).

Сигналы D0, D1 являются сигналами режима работы узла (D1=1,D0=1 — автоколебательный, D1=1, D0=0 — ждущий, D1=0,D0=0 останов). Сигнал С1 инверсный и является сигналом записи команды с входов D1, D0 в регистр микрокоманд. Сигнал C2 инверсный сигнал старта работы узла. |

Согласно варианту задания, необходимо реализовать данное устройство тремя различными способами:

1. На основе сдвигающего регистра.

Для реализации требуется 12 корпусов микросхем с общей площадью.

Sобщ=146,25*10+161,25+191,25=1815мм2.

2. На основе реверсивного сдвигающего регистра.

Для реализации требуется 11 корпусов микросхем с общей площадью.

Sобщ=146,25*6+161,25*4+191,25=1713,75 мм².

3. На основе счетчика Джонсона.

Для реализации требуется 15 корпусов микросхем с общей площадью.

Sобщ=146,25*14+161,25*3=2531,25 мм².

Из трех возможных реализаций данного узла наиболее подходящими по критерию оптимизации (Smin) является схема на основе реверсивного сдвигающего регистра.

Описание возможных вариантов реализации разрабатываемого узла на уровне функциональных схем

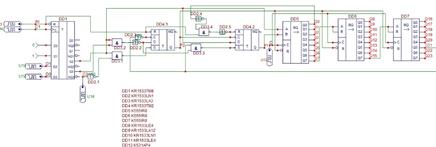

На рисунке 2представлена схема распределителя импульсов на основе сдвигающего регистра. Данный вид реализации распределителя импульсов принципиально отличается от остальных тем, что в нем не нужно применять дешифратор послесчетчика тактов. Требуемая цепочка импульсов для логической схемы получается на самом счетчике тактов.

Счетчик тактов реализован на 24разрядномсдвигающемрегистре. На первом такте в первый разряд регистра записывается единица, которая с выхода регистра поступает на управляющий автомат, который на следующих тактах будет записывать в первый разряд регистра ноль, сдвигая тем самым единицу в старший разряд. Появление единицы в 22разрядесигнализирует о том, что цикл закончен.

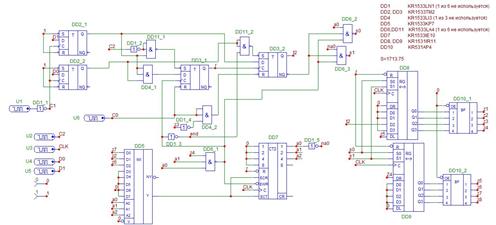

На рисунке 3представлена схема на основе реверсивного сдвигающего регистра. При работе схемы в «Автоколебательном» или «Ждущем» режиме в D-триггер DD21 записывается «1». Вследствие чего, положительный фронт сигнала возникающего на выходе этого триггера устанавливает в «1» D-триггер DD32, который в свою очередь устанавливает реверсивный сдвигающий регистр DD8 в начальное состояние (запись «1» в третий разряд). 4-разрядный счетчик DD7 управляют направлением сдвига реверсивного регистра, путем подачи соответствующих сигналов на входы S0 и S1 через комбинационную схему. Буферные элементы на выходе формируют выходные сигналы z1-z9 и обеспечивают необходимый коэффициент нагрузки.

На рисунке 4представлена схема распределителя импульсов на основе счетчика Джонсона. В данном варианте реализации в качестве счетчика тактов применен счетчик Джонсона. Счетчик Джонсона строится на триггерах, количество которых вычисляется по формуле:

n = N/2+k.

где: n — количество триггеров в счетчике;

N — количество тактов счета;

k — равняется 0 при нечетном количестве тактов и 1 при четном.

Состояния счетчика передаются на дешифратор, который преобразует состояния счетчика Джонсона в цепочку импульсов на своих выходах.

Наличие отрицательного сигнала на выходесигнализирует о завершении цикла счета.

Выбор наилучшего варианта реализации по заданному критерию Ток всех схем иэлементов схем приведен ниже:

КОЛЬЦЕВОЙ СЧЕТЧИК. | ||||

Микросхема. | Серия. | Корпус. | Кол-во. | |

DD1. | KР1533ТМ8. | DIP16. | 161,25. | |

DD2, DD10. | K1533ЛН1. | DIP14. | 146,25*2. | |

DD3. | KР1533ЛА3. | DIP14. | 146,25. | |

DD4. | KР1533TM2. | DIP14. | 146,25. | |

DD5,DD6,DD7. | K555ИР8. | DIP14. | 146,25*3. | |

DD8, DD11. | K155ЛЕ4. | DIP14. | 146,25*2. | |

DD9. | KР1533ЛА12. | DIP14. | 146,25. | |

DD12. | К531АП4. | DIP20. | 191,25. | |

Sобщ.: |

Sобщ=146,25*10+161,25+191,25=1815мм2.

РЕВЕРСИВНЫЙ РЕГИСТР. | ||||

Микросхема. | Серия. | Корпус. | Кол-во. | |

DD1. | КР1533ЛН1. | DIP14. | 146,25. | |

DD2, DD3. | КР1533ТМ2. | DIP14. | 146,25*2. | |

DD4. | КР1533ЛИ3. | DIP14. | 146,25. | |

DD5. | КР1533КП7. | DIP16. | 161,25. | |

DD6, DD11. | КР1533ЛА4. | DIP14. | 146,25*2. | |

DD7. | KР1533ИЕ10. | DIP16. | 161,25. | |

DD8, DD9. | KР1531ИР11. | DIP16. | 161,25*2. | |

DD10. | К531АП4. | DIP20. | 191,25. | |

Sобщ.: | 1713,75. |

Sобщ=146,25*4+161,25*4+191,25=1713,25 мм².

СЧЕТЧИК ДЖОНСОНА. | ||||

Микросхема. | Серия. | Корпус. | Кол-во. | |

DD1,DD2. | КР1533ТМ2. | DIP14. | 146,25*2. | |

DD3. | КР1533ЛН1. | DIP14. | 146,25. | |

DD4. | КР1533ЛР11. | DIP14. | 146,25. | |

DD5-DD7. | КР1533ТМ8. | DIP16. | 161,25*3. | |

DD8-DD13. | КР1533ЛA3. | DIP14. | 146,25*6. | |

DD14. | К155ЛА12. | DIP14. | 146,25. | |

DD15-DD17. | К155ЛА6. | DIP14. | 146,25*3. | |

Sобщ.: | 2238,75. |

Sобщ=146,25*14+161,25*3=2238,75 мм².

4 Описание используемых интегральных схем При реализации оптимальной схемы использовались схемы серии 1533, 155 и555.

Элемент. | Кол-во. | Тип ИС. | Кол-во схем. | Корпус. ИС. | Площадь. |

НЕ. | КР1533ЛН1. | DIP14. | 146,25. | ||

D-триггер | КР1533ТМ2. | DIP14. | 292,5. | ||

3И. | КР1533ЛИ3. | DIP14. | 146,25. | ||

мультиплексор | КР1533КП7. | DIP16. | 161,25. | ||

3И-НЕ. | КР1533ЛА4. | DIP14. | 292,5. | ||

счетчик. | KР1533ИЕ10. | DIP16. | 161,25. | ||

регистр | KР1531ИР11. | DIP16. | 322,5. | ||

интерфейсный эл-т. | К531АП4. | DIP20. | 191,25. | ||

ИТОГО: | 1713,75. |

Серия 531-мощные ТТЛШ повышенного быстродействия.

Серия 1533 — микросхемы серии 1533 схожи по своим свойствам и структуре с зарубежным аналогом 74АLS, где используются транзисторы «Изопланар 2», где граничная частота достигает 5Ггц, в то время как у обычного транзистора она не достигает и 1.7Ггц. Серии данной архитектуры потребляют малую мощность 1.2мВТ и переключаются с задержкой tз.ср.=4нс. Серию 1533 относят к архитектуре (ТТЛШ), в то время как за рубежом аналоги данной серии АLS относят к более высокому порядку. Дословно АLS: А — сверхбыстрые, L — маломощные, S — с барьером Шоттки.

Серия 1531 — маломощные ТТЛШ повышенного быстродействия.