Динамическая память.

Иерархическая организация памяти

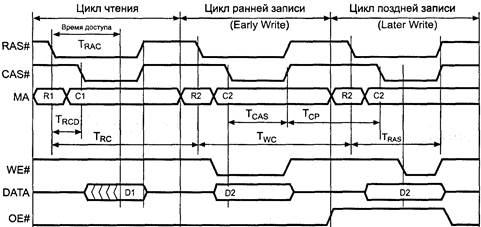

Ячейки организуются в двумерные матрицы, и для обращения к ячейке требуется последовательно подать два выбирающих сигнала — RAS# (Row Access Strobe, строб строки) и CAS# (Column Access Strobe, строб столбца). Временная диаграмма циклов чтения традиционной динамической памяти приведена на рисунке (циклы записи для простоты здесь рассматривать не будем). Микросхемы динамической памяти традиционно… Читать ещё >

Динамическая память. Иерархическая организация памяти (реферат, курсовая, диплом, контрольная)

Теперь посмотрим на оперативную память изнутри. На протяжении уже трех десятилетий в качестве основной памяти используют массивы ячеек динамической памяти. Каждая ячейка содержит всего лишь один КМОП-транзистор (комплементарные полевые транзисторы), благодаря чему достигается высокая плотность упаковки ячеек при низкой цене. Запоминающим элементом у них является конденсатор (емкость затвора), и ячейка может помнить свое состояние недолго — всего десятки миллисекунд. Для длительного хранения требуется регенерация — регулярное «освежение» (refresh) памяти, за что эта память и получила название «динамическая» — DRAM (Dynamic RAM).

Динамическая память получила свое название от принципа действия ее запоминающих ячеек, которые выполнены в виде конденсаторов, образованных элементами полупроводниковых микросхем. Несколько упрощая описание физических процессов, можно сказать, что при записи логической единицы в ячейку конденсатор заряжается, при записи нуля — разряжается. Схема считывания разряжает через себя этот конденсатор, и, если заряд был ненулевым, выставляет на своем выходе единичное значение и подзаряжает конденсатор до прежнего уровня. При отсутствии обращения к ячейке со временем за счет токов утечки конденсатор разряжается и информация теряется, поэтому такая память требует постоянной периодической подзарядки конденсаторов (обращения к каждой ячейке) — память может работать только в динамическом режиме. Этим она принципиально отличается от статической памяти, реализуемой на триггерных ячейках и хранящей информацию без обращений к ней сколь угодно долго (при включенном питании). Благодаря относительной простоте ячейки динамической памяти на одном кристалле удается размещать миллионы ячеек и получать самую дешевую полупроводниковую память достаточно высокого быстродействия с умеренным энергопотреблением, используемую в качестве основной памяти компьютера. Запоминающие ячейки микросхем DRAM организованы в виде двумерной матрицы. Адрес строки и столбца передается по мультиплексированной шине адреса МА (MultiplexedAddress) и стробируется по спаду импульсов RAS# (RowAccessStrobe) и CAS# (ColumnAccessStrobe). Состав сигналов микросхем динамической памяти приведен в табл. 6.

Таблица 6. Сигналы микросхем динамической памяти.

Сигнал. | Назначение. | |

RAS#. | RowAccessStrobe — строб выборки адреса строки. По спаду сигнала начинается любой цикл обращения, низкий уровень сохраняется на все время цикла. Перед началом следующего цикла сигнал должен находиться в неактивном состоянии (высокий уровень) не менее, чем время предварительного заряда RAS (ТRP — RASprecliargetime). | |

CAS#. | ColumnAccessStrobe — строб выборки адреса столбца. По спаду сигнала начинается цикл записи или чтения, минимальная длительность (ТCAS) определяется спецификацией быстродействия памяти. Минимальная длительность неактивного состояния между циклами (высокий уровень) должна быть не менее чем время (TCPCASprechargetime) предварительного заряда CAS. | |

MAi. | MultiplexedAddress — мультиплексированные линии адреса. Во время спада сигнала RAS# на этих линиях присутствует адрес строки, во время спада CAS# — адрес столбца. Адрес должен устанавливаться до спада соответствующего строба и удерживаться после него еще некоторое время. Микросхемы с объемом 4 М ячеек могут быть с симметричной организацией — 11 бит адреса строк и 11 бит адреса колонок или асимметричными —12×10 бит соответственно. | |

WE#. | WriteEnable — разрешение записи. Данные записываются в выбранную ячейку либо по спаду CAS# при низком уровне WE# (EarlyWrite — ранняя запись, обычный вариант), либо по спаду WE# при низком уровне CAS# (DelayedWrite — задержанная запись). Переход WE# в низкий уровень и обратно при высоком уровне CAS# записи не вызывает, а только переводит выходной буфер EDODRAM в высокоимпедансное состояние. | |

ОЕ#. | OutputEnable — разрешение открытия выходного буфера при операции чтения. Высокий уровень сигнала в любой момент переводит выходной буфер в высокоимпедансное состояние. | |

DB-In. | DataBitInput — входные данные (только для микросхем с однобитной организацией). | |

DB-Out. | DataBitOutput — выходные данные (только для микросхем с однобитной организацией). Выходные буферы стандартных микросхем открыты только при сочетании низкого уровня сигналов RAS#, CAS#, OE# и высокого уровня WE#; при невыполнении любого из этих условий буферы переходят в высокоимпедансное состояние. У микросхем EDO выходные буферы открыты и после подъема CAS#. Логика управления предусматривает возможность непосредственного объединения выходов нескольких микросхем. | |

DQx. | DataBit — объединенные внутри микросхемы входные и выходные сигналы данных (объединение экономит количество выводов для микросхем с многобитной организацией). | |

N.C. | NoConnection — свободный вывод. | |

Выбранной микросхемой памяти является та, на которую во время активности (низкого уровня) сигнала RAS# приходит сигнал CAS# (тоже низким уровнем). Тип обращения определяется сигналами WE# и CAS#. Временная диаграмма «классических» циклов записи и чтения приведена на рис. 50. Как из нее видно, при чтении данные на выходе относительно начала цикла (сигнала RAS#) появятся не раньше, чем через интервал ТRAC, который и является временем доступа.

Рисунок 50. Временные диаграммы чтения и записи динамической памяти.

Ячейки организуются в двумерные матрицы, и для обращения к ячейке требуется последовательно подать два выбирающих сигнала — RAS# (Row Access Strobe, строб строки) и CAS# (Column Access Strobe, строб столбца). Временная диаграмма циклов чтения традиционной динамической памяти приведена на рисунке (циклы записи для простоты здесь рассматривать не будем). Микросхемы динамической памяти традиционно имеют мультиплексированную шину адреса (MA). Во время действия RAS# на ней должен быть адрес строки, во время действия CAS# — адрес столбца. Информация на выходе шины данных относительно начала цикла (сигнала RAS#) появится не раньше, чем через интервал TRAC, который называется временем доступа. Есть также минимальная задержка данных относительно импульса CAS# (TCAC), и минимально необходимые интервалы пассивности сигналов RAS# и CAS# (времена предзаряда). Все эти параметры и определяют предел производительности памяти. Ключевой параметр микросхем — время доступа — за всю историю удалось улучшить всего на порядок — с сотен до нескольких десятков наносекунд. За меньший исторический период только тактовая частота процессоров x86 выросла на 2 порядка, так что разрыв между потребностями процессоров и возможностями ячеек памяти увеличивается. Для преодоления этого разрыва, во-первых, увеличивают разрядность данных памяти, а во-вторых, строят вокруг массивов ячеек памяти разные хитрые оболочки, ускоряющие процесс доступа к данным. Все, даже «самые модные», типы памяти — SDRAM, DDR SDRAM и Rambus DRAM имеют запоминающее ядро, которое обслуживается описанным выше способом.