Определение форматов команд процессора

Приведенный образец составления таблицы кодирования форматов команд позволяет формализовать описание содержания всех операций, реализуемых процессором, и унифицировать множество принимаемых условных обозначений и сокращений. Для удобства последующей распаковки кода формата команды разряды с 9-го по 15-й делаем «пустыми», для того чтобы второе поле непосредственного операнда I, как и в предыдущей… Читать ещё >

Определение форматов команд процессора (реферат, курсовая, диплом, контрольная)

Основная задача на данном этапе — определение разрядностей основных шин и блоков, в частности: шины данных, шины адреса, шины управления, АЛУ, ОП, УУ, Рг, а также разрядностей команд и данных и количества регистров, обеспечивающих выполнение заданного набора операций.

Первый этап — это определение разрядностей основных коммуникационных элементов разрабатываемого процессора: шины данных (ШД), шины адреса (ША) и шины управления (ШУ).

Разрядность ШД определяется из варианта задания. В задании задана разрядность шины данных. Она равна 64. Это и будет разрядностью шины данных, то есть ШД (63−0).

Для определения разрядности ША должны быть заданы параметры запоминающего устройства, в частности разрядность слова и емкость.

Оценку разрядности ША можно выполнить за два этапа. На первом этапе необходимо произвести арифметическую операцию деления заданной емкости запоминающего устройства на разрядность его слова; при этом необходимо учитывать, что емкость памяти задана в килобайтах. Выполнив операцию 316*1024/32, получим, что память содержит 512 ячеек. На следующем этапе необходимо подобрать ближайшую наименьшую степень двойки, достаточную для того, чтобы записать в двоичной системе счисления полученное число ячеек. Такой степенью является число 9, то есть 29. Таким образом, разрядность шины адреса должна быть равна 9. Получаем ША (8−0).

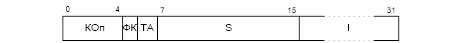

Для нахождения разрядности шины управления в первую очередь необходимо составить формат команды. В формате SI команда представляется следующим образом:

Коп. | ФК. | ТА. | S. | I. | |

Так как количество операций, которые необходимо реализовать в разрабатываемом устройстве, равно 28, то для того, чтобы их закодировать, необходимо 5 двоичных разрядов как наименьшей степени двойки, достаточной для двоичного кодирования данного количества операций. После выбора количества разрядов КОп необходимо закодировать все операции системы команд. Для этого составляем таблицу, в которой проставляем коды заданных команд (табл. 1).

Таблица 1 — Кодирование команд

Тип операции. | Код. | Тип операции. | Код. | |

Сложение. | Запись в ЗУ. | |||

Вычитание. | Чтение из ЗУ. | |||

Умножение. | Запись в стек. | |||

Деление. | Чтение из стека. | |||

ИЛИ. | Сложение со стеком. | |||

И. | Вычитание из стека. | |||

Сумма по модулю 2. | Запись в ВУ. | |||

Условный переход, если >0. | Чтение из ВУ. | |||

Условный переход, если <0. | Остановка. | |||

Условный переход по =0. | Разрешение прерывания. | |||

Условный переход по переполнению. | Запрещение прерывания. | |||

Безусловный переход. | Возврат из прерывания. | |||

Переход к подпрограмме. | Загрузка регистра базы. | |||

Выход из подпрограммы. | Загрузка указателя стека. | |||

Так как в задании дано два формата команды, то, чтобы их закодировать, достаточно одного бита. Выбираем следующие коды заданных форматов: SI — ФК=0, для формата RI — ФК=1.

Для того чтобы закодировать содержимое поля ТА, необходимо два разряда, так как задано три типа адресации. При этом необходимо выбрать коды всех заданных видов ТА. Примем для прямой адресации код ТА=0., для косвенной — ТА=1.

После кодирования содержимых этих полей необходимо переходить к выбору длин остальных полей. Поле S, то есть адрес ячейки оперативной памяти, имеет разрядность 9, так как шина адреса имеет разрядность 9. Последнее поле I — это непосредственный операнд, который имеет разрядность 16 в соответствии с разрядностью данных по заданию.

Получаем следующий формат команды:

Полученный формат команды имеет длину 32 бит, отсюда получаем разрядность шины управления, так как она равна разрядности формата команды. Таким образом получаем ШУ (15−0).

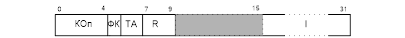

Для команд формата RI ситуация выглядит иначе. Здесь формат команды будет немного другим. Поля формата будут практически одинаковы, кроме поля S. Для выбора разрядности поля R сначала необходимо выбрать число регистров общего назначения (РОН). В данном курсовом проекте вполне достаточно восьми регистров. Следовательно, для адресации к восьми регистрам необходимо иметь три разряда внутренней шины адреса АЛУ: R=3. Разрядность поля I будет равна заданной разрядности шины данных, так как поле I является полем непосредственного операнда: I=64. Отсюда получаем следующий формат команды для варианта RI:

Для удобства последующей распаковки кода формата команды разряды с 9-го по 15-й делаем «пустыми», для того чтобы второе поле непосредственного операнда I, как и в предыдущей команде, начиналось с 16-го бита и заканчивалось 31-м битом.

После определения форматов команд процессора необходимо составить содержательную таблицу кодирования всех вариантов форматов команд (табл. 2).

Таблица 2 — Кодирование форматов команд.

Код операции. | Формат команды. | Тип адресации (ТА). | Код ТА. | Содержание операции. | |

Арифметические. | |||||

Сложение 0. | RI. | П. | A1.A2:= POH[R] +I; | ||

К. | A1.A2:= OP[POH[R]] + I; | ||||

SI. | П. | A1.A2:= OP[S] + I; | |||

К. | A1.A2:= OP[OP[S]] + I; | ||||

Вычитание 1. | RI. | П. | A1.A2:=POH[R]-I; | ||

К. | А1.A2:= OP[POH[R]] - I; | ||||

SI. | П. | A1.A2:= OP[S] - I; | |||

К. | A1.A2:= OP[OP[ S]] - I; I. | ||||

Умножение. | RI. | П. | A1.A2:= POH[R]*I; | ||

К. | A1.A2:=OP[POH[R]]*I; | ||||

SI. | П. | A1.A2:= OP[S]*I; | |||

К. | A1.A2:=OP[OP[S]]*I; | ||||

Деление. | RI. | П. | A1.A2:=POH[R] / I; | ||

К. | A1.A2:=OP[POH[R]]/I; | ||||

SI. | П. | A1.A2:=OP[S] / I; | |||

К. | A1.A2.В1.В2:=OP[OP[S]]/I; | ||||

Логические. | |||||

Дизъюнкция 100. | RI. | П. | A1.A2:=POH[R]vI; | ||

К. | A1.A2:=OP[POH[R]]vI; | ||||

SI. | П. | A1.A2:= OP[S]vI; | |||

К. | A1.A2:=OP[OP[S]]vI; | ||||

Конъюнкция. | RI. | П. | A1.A2:=POH[R]ЛI; | ||

К. | A1.A2:= OP[POH[R]]ЛI; | ||||

SI. | П. | A1.A2:= OP[S] Л I; | |||

К. | A1.A2:=OP[OP[S]]ЛI; | ||||

Сложение пo модулю.

| RI. | П. | A1.A2:=POH[R]_I; | ||

К. | A1.A2:= OP[POH[R]] _I; | ||||

SI. | П. | А1.A2:= OP[S] _ I; | |||

К. | A1.A2:=OP[OP[S]] _I. | ||||

УП пo > 0 111. | RI. | П. | if (SF = 0) and (ZF = 0) then PC:=I. | ||

К. | |||||

SI. | П. | ||||

К. | |||||

УП пo < 0 1 000. | RI. | П. | if SF = 1 thenPC:=I. | ||

К. | |||||

SI. | П. | ||||

К. | |||||

УП по = 1 001. | RI. | П. | If ZF = l then PC := I. | ||

К. | |||||

SI. | П. | ||||

К. | |||||

УП по переполнению. | RI. | П. | If OF = l then PC := I. | ||

К. | |||||

SI. | П. | ||||

К. | |||||

Безус; ловный переход. | RI. | П. | PC := I. | ||

К. | |||||

SI. | П. | ||||

К. | |||||

Вызов подпрограммы. | RI. | П. | SP := SP — 1,. OP[SP] := PC+2,. PC := I. | ||

К. | |||||

SI. | П. | ||||

К. | |||||

Возврат из-под; программы 1 101. | RI. | П. | PC := OP[SP],. SP := SP + 1. | ||

К. | |||||

SI. | П. | ||||

К. | |||||

Операции с запоминающим устройством. | |||||

Запись в ЗУ. | RI. | П. | POH[R] := A1. A2. | ||

К. | OP[POH[R]] := I. | ||||

SI. | П. | OP[S] :=A1.A2. | |||

К. | OP[OP[S]]: =I. | ||||

Чтение из ЗУ 1 111. | RI. | П. | A1.A2:= POH[R]. | ||

К. | A1.A2:= OP[POH[R]]. | ||||

SI. | П. | A1.A2:= OP[S]. | |||

К. | A1.A2:= OP[OP[S]]. | ||||

Операции со стеком. | |||||

Запись 10 000. | RI. | П. | SP := SP — 2, OP[SP] := POH[R]. | ||

К. | |||||

SI. | П. | SP := SP — 2, OP[SP] := A1. A2. | |||

К. | |||||

Чтение 10 001. | RI. | П. | POH[R] := OP[SP], SP := SP + 2. | ||

К. | |||||

SI. | П. | A1.A2:= OP[SP], SP := SP + 2. | |||

К. | |||||

Сложение со стеком 10 010. | RI. | П. | OP[SP] := OP[SP] + POH[R]. | ||

К. | |||||

SI. | П. | OP[SP]: =OP[SP]+A1.A2. | |||

К. | |||||

Вычита; ние из стека. | RI. | П. | OP[SP] := OP[SP] - POH[R]. | ||

К. | |||||

SI. | П. | OP[SP] := OP[SP] - A1. A2. | |||

К. | |||||

Операции с внешними устройствами. | |||||

Запись в ВУ 10 100. | RI. | П. | RgED := POH[R]. | ||

К. | |||||

SI. | П. | RgED := OP[S]. | |||

К. | |||||

Чтение изВУ 10 101. | RI. | П. | POH[R] := RgED. | ||

К. | |||||

SI. | П. | OP[S] := RgED. | |||

К. | |||||

Системные операции. | |||||

Останов. | RI. | П. | WF := U. | ||

К. | |||||

SI. | П. | ||||

К. | |||||

Разре; шение преры; вания. | RI. | П. | IF := 1. | ||

К. | |||||

SI. | П. | ||||

К. | |||||

Запрещение прерывания 11 000. | RI. | П. | IF := 0. | ||

К. | |||||

SI. | П. | ||||

К. | |||||

Возврат из пре; рывания. | RI. | П. | PC := OP[SP], SP := SP + 1. RgF:=OP[SP], SP:=SP+1. | ||

К. | |||||

SI. | П. | ||||

К. | |||||

Загрузка регистра базы (В). | RI. | П. | B:=POH[R]. | ||

К. | |||||

SI. | П. | В := OP[S]. | |||

К. | |||||

Загрузка указателя стека (SP). | RI. | П. | SP := POH[R]. | ||

К. | |||||

SI. | П. | SP := OP[S]. | |||

К. |

Примечание. Сокращения наименований и условные обозначения содержимого полей, ячеек ОП и регистров следующие: R, S — значения полей из кода инструкции; ОР — операнд из памяти; A1. A2 -аккумулятор, состоящий из 2 8-разрядных регистров; SP — регистр — указатель стека; PC — регистр — программный счетчик; RIадресация «регистр — непосредственный операнд»; SI — адресация «ячейка оперативной памяти — непосредственный операнд»; RgEDрегистр внешнего устройства; RgF — регистр флагов; WF — флаг пуска-останова процессора; SF — флаг знака; OF — флаг переполнения; ZF — флаг нуля; [address] - операнд из ячейки с адресом address; Врегистр базы; IF — флаг прерывания.

Приведенный образец составления таблицы кодирования форматов команд позволяет формализовать описание содержания всех операций, реализуемых процессором, и унифицировать множество принимаемых условных обозначений и сокращений.