Техническая реализация интерфейса обмена данными с прерыванием программы

Техническая реализация многоуровневых векторных прерываний в ЭВМ на основе единого магистрального канала обмена данными (приоритетная цепочка). Интерфейсы нескольких ВУ могут быть подсоединены параллельно к одной линии ЗП магистрали ЭВМ таким образом, что все запросы поступают по одной и той же линии. Для идентификации источника запроса ЦП посылает сигнал разрешения прерывания (РП) в интерфейсы… Читать ещё >

Техническая реализация интерфейса обмена данными с прерыванием программы (реферат, курсовая, диплом, контрольная)

Существуют два варианта технической реализации схемы учета приоритетов и схемы формирования адреса вектора прерываний интерфейса обмена данными с прерыванием программы: приоритетная цепочка и программируемая логика управления приоритетами прерываний. Первый вариант реализован в ЭВМ на основе единого магистрального канала (семейство Macintosh), второй — в ЭВМ с изолированными магистральными каналами обмена (семейство IBM).

Техническая реализация многоуровневых векторных прерываний в ЭВМ на основе единого магистрального канала обмена данными (приоритетная цепочка). Интерфейсы нескольких ВУ могут быть подсоединены параллельно к одной линии ЗП магистрали ЭВМ таким образом, что все запросы поступают по одной и той же линии. Для идентификации источника запроса ЦП посылает сигнал разрешения прерывания (РП) в интерфейсы. Сигнал РП поступает от ЦП к ВУ последовательно по линии РП (рис. 5.23).

Вначале сигнал РП поступает на ВУ 1 (расположенное физически ближе к ЦП). Если ВУ1 не требовало прерывания программы, его схема учета приоритетов пропускает сигнал РП к следующему ВУ и т. д.

Рис. 5.23. Блок-схема алгоритма идентификации источника запроса прерывания в ЭВМ на основе единого магистрального канала.

В первом устройстве в цепочке (ближайшем к ЦП), которое посылало ЗП:

- • схема учета приоритетов поглощает сигнал РП;

- • схема формирования АВП выдает на ШД адрес вектора прерывания и сбрасывает ТРИ в регистре управления интерфейсом.

Таким образом, схема учета приоритетов ВУ блокирует сигнал РП, если ВУ требует прерывание программы или пропускает его к следующему ВУ, если данное ВУ не устанавливало сигнал ЗП процессору. Устройства, расположенные физически ближе к ЦП, имеют больший приоритет обслуживания.

Адрес вектора прерывания обычно представляет собой восьмибитовое слово, которое поступает на ШД с формирователя адреса вектора прерываний (ФАВН) интерфейса ВУ. Поскольку ВП занимает 4 байта в области адресов 0. 255, то имеется возможность передать 64 различных АВП — О, 4, 8,. 252.

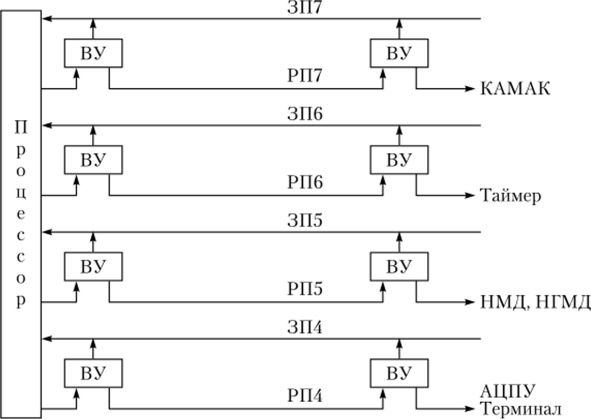

Формирователь адреса вектора прерываний представляет собой комбинационную схему, на вход которой поступает сигнал РП от ЦП, а с выхода на шину данных ЭВМ поступает определенная для данного ВУ комбинация «О» и «1». В ЭВМ на основе единого магистрального канала имеется несколько линий «ЗП — РП» и, следовательно, несколько приоритетных уровней прерываний. Это позволяет организовать многоуровневые вложенные векторные прерывания. Число линий «ЗП — РП» в разных моделях ЭВМ может меняться от 1 до 7. В большинстве ЭВМ имеются четыре приоритетных уровня (рис. 5.24).

Количество ВУ, подключаемых к одной паре линий «ЗШ — РШ», не ограничено. Каждой паре линий «ЗШ — РШ» соответствует свой уровень приоритета обслуживания ВУ. Приоритеты линий фиксированы. Линия «ЗП7» имеет наивысший приоритет (7), а линия «ЗП1» — низший (1) приоритет обслуживания. Внешние устройства, подсоединенные к к-й линии, имеют к-й приоритет обслуживания.

Рис. 5.24. Многоуровневая схема идентификации источника запроса прерывания

При поступлении запроса по одной из линий «ЗП7 — 3111» процессор сравнивает приоритет линии с приоритетом, указанным в РСП. Если приоритет линии «ЗШ» выше приоритета процессора, то процессор выдает сигнал РШ по соответствующей линии и начинает исполнять процедуру прерывания. При равенстве приоритетов линии «ЗШ» и процессора прерывания программы не происходит. Линия «ЗШ» остается возбужденной, т. е. прерывание «ждет очереди». Когда приоритет процессора станет ниже приоритета линии, процессор переходит к обслуживанию запроса с данной линии «311/?».

Разработчик АС имеет возможность подсоединить ВУ к любой линии ЗП. Программист имеет возможность присвоить оперативной программе обслуживания ВУ любой приоритет, указывая его в векторе прерывания. Однако обычно программа обслуживания прерывания имеет тот же приоритет, что и инициализирующее ее ВУ.

Основная особенность такого способа реализации прерываний — уровни приоритетов ВУ и АВП устанавливаются аппаратными средствами интерфейса и не могут меняться в процессе работы системы.

Техническая реализация многоуровневых векторных прерываний в ЭВМ на основе изолированных каналов обмена данными (семейства IBM PC). В автоматизированных системах на основе ЭВМ с изолированными каналами обмена данными для управления прерываниями от ВУ используется программируемая логика управления приоритетами прерываний (ПЛУПП). В качестве ПЛУПП в ЭВМ семейства IBM применена типовая БИС программируемого контроллера прерываний (ПКП) Intel 8259A.

Технические характеристики ПКП:

- • число приоритетных уровней запросов прерываний от внешних устройств — 8;

- • число приоритетных уровней запросов прерываний может быть расширено до 64 путем каскадного соединения микросхем ПКИ;

- • корпус 28 pin (выводов микросхемы), питание +5 В, таймера нет.

В ЭВМ семейства IBM АТ имеются два каскадно-включенных ПКП. Схемы учета приоритетов и схемы формирования АВП перенесены из интерфейсов ВУ в БИС ПКП. В интерфейсе осталась только схема формирования АВП.

Основное отличие ПЛУПП от приоритетной цепочки в том, что режим обслуживания запросов от ВУ, уровни приоритетов и АВП устанавливаются программным путем и могут быть изменены в процессе работы системы.

Программируемые режимы обслуживания ВУ:

- 1) вложенные прерывания. Каждому из восьми входов запросов прерываний IR0. IR7 назначается фиксированный приоритет в порядке убывания, и запрос с большим приоритетом может прерывать обслуживание запросов с меньшим приоритетом. Иными словами, запрос от входа IRi могут прерывать запросы от входов IR0. IR (i- 1);

- 2) круговой (циклический) приоритет. Как и в предыдущем случае, каждому входу IR0. IR7 назначается определенный приоритет, но после появления запроса прерывания IRi и выполнения программы его обслуживания приоритеты изменяются в круговом порядке таким образом, что последний обслуженный вход IRi будет иметь низший приоритет. Если, например, обслужен запрос IR4, низший приоритет назначается IR4, и получается следующий порядок приоритетов: IR5, IR6, IR7, IRO, IR1, IR2, IR3, IR4;

- 3) адресуемые приоритеты. Режим аналогичен предыдущему, но допускает программное определение входа IRi, которому назначается низший приоритет;

- 4) режим опроса. В этом режиме прерывания процессора запрещаются, а требующее обслуживания В У определяется считыванием состояния контроллера;

- 5) незамаскированные запросы обслуживаются в порядке их поступления.