Структура МП Intel 8086

Каждый из регистров данных кроме арифметических функций имеет также и специальное назначение в некоторых командах. Так, через регистр АХ (accumulator— аккумулятор) осуществляется передача и прием данных между микропроцессором и внешними устройствами в командах ввода/ вывода. Регистр ВХ (base — база) может использоваться для хранения базового двоичного числа, используемого при вычислениях адресов… Читать ещё >

Структура МП Intel 8086 (реферат, курсовая, диплом, контрольная)

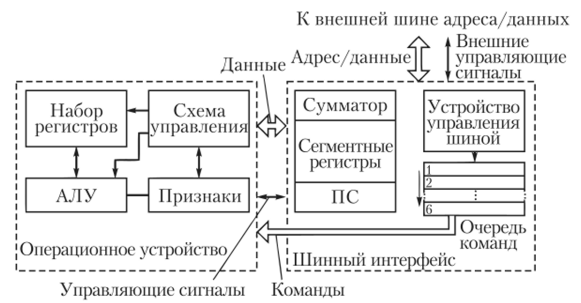

Как известно, перед тем как МП начинает выполнять команду, он должен ее считать из памяти программ. В первых МП процессы чтения очередной команды и ее выполнения производились последовательно друг за другом. В МП Intel 8086 впервые был применен принцип совмещения во времени выполнения очередной команды с выборкой следующей. Этот принцип получил название конвейерного и был положен в основу работы всех последующих типов МП. Для этого МП (рис. 4.12) разделен на два сравнительно независимых устройства: операционное устройство (ОУ) и шинный интерфейс (ШИ).

ОУ осуществляет выполнение операций (математических, логических и т. д.), заданных командой. Шинный интерфейс выбирает команды из памяти программ, считывает операнды из памяти или ВУ, записывает результаты. Оба устройства работают параллельно, и пока ОУ выполняет операцию, ШИ подготавливает к выполнению следующую команду.

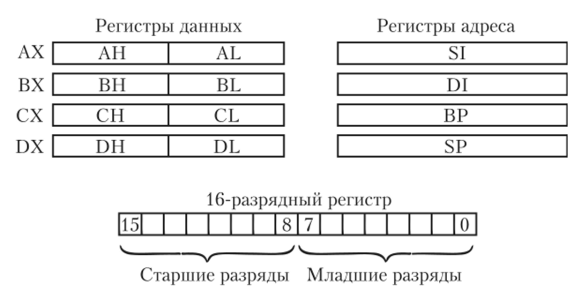

ОУ содержит набор 16-разрядных регистров, доступных при программировании микропроцессора, т. е. регистров для занесения или извлечения информации, но командам программы. В состав ОУ входят регистры данных и адресные регистры (рис. 4.13). Регистры данных могут использоваться для хранения операндов и результатов операций. Каждый из них можно разделить и использовать как два независимых 8-разрядных регисгра. В этом случае старшая половина регистра обозначается буквой Н (high), а младшая — L (low).

Рис. 4.12. Структура микропроцессора Intel 8086.

Рис. 4.13. Внутренние регистры микропроцессора.

Каждый из регистров данных кроме арифметических функций имеет также и специальное назначение в некоторых командах. Так, через регистр АХ (accumulator— аккумулятор) осуществляется передача и прием данных между микропроцессором и внешними устройствами в командах ввода/ вывода. Регистр ВХ (base — база) может использоваться для хранения базового двоичного числа, используемого при вычислениях адресов ячеек ОЗУ. Регистр СХ (counter — счетчик) в некоторых командах используется как счетчик. Регистр DX (data — данные) в некоторых командах ввода/вывода содержит адрес регистра внешнего устройства — порта ввода/вывода.

Адресные регистры могут использоваться только для хранения 16-разрядных двоичных чисел, используемых при вычислении адресов ячеек ОЗУ. Регистры SI и DI называют индексными (index), а ВР и SP — указательными (pointer — указатель). Регистры SI, DI и ВР используются во многих командах для адресации ячеек ОЗУ и являются универсальными адресными регистрами. Регистр SP — специальный регистр, предназначенный для работы со стеком (stack pointer — указатель стека).

В состав ОУ также входят АЛУ, буферные регистры, регистр состояния процессора и схема управления. АЛУ, как и во многих МП, обеспечивает выполнение арифметических, логических и сдвиговых операций, формируя при этом признаки результата. Буферные регистры используются для временного хранения операндов и результата операции во время выполнения команды. Эти регистры недоступны для пользователя. Регистр состояния процессора осуществляет запись признаков результата — флажков, а также хранение флажков условий, от которых зависит выполнение некоторых специальных функций.

Каждому признаку соответствует свой флажок. Весь набор различных условий в командах условного перехода формируется на основе анализа содержимого разрядов слова состояния процессора — флажков. Таких флажков всего шесть. Это флажок знака, соответствующего старшему биту результата (1 — отрицательный, 0 — положительный); флажок нуля — если результат равен нулю; флажок паритета — если в младших битах четное число единиц; флажок переноса — если возникает перенос (заем) из старшего бита; флажок вспомогательного переноса — если возникает перенос (заем) из третьего бита при выполнении операций в двоично-десятичной арифметике; флажок переполнения — если результат не помещается в установленном диапазоне.

Схема управления осуществляет дешифровку команды и формирует необходимые управляющие сигналы. О У изолировано от внешней шины, поэтому обмен данными и адресами между О У и ШИ осуществляется по внутренней шине.

ШИ выполняет все операции обмена данными с памятью и ВУ, но требованию ОУ. ШИ содержит устройство управления шиной, набор адресных регистров, включая ПС и специальные сегментные регистры, сумматор и набор регистров, называемых очередью команд.

Устройство управления шинами обеспечивает взаимодействие МП с внешними шинами. Когда ОУ занято выполнением команд и не требует выборки операндов из памяти или В У, ШИ самостоятельно выбирает из памяти программ очередные команды. Эти команды хранятся во внутренней регистровой памяти ШИ — очереди команд (см. рис. 4.12). Длина очереди — 6 байт. По мере выполнения команд очередь движется и в ней появляется свободное место. При этом ШИ обращается к памяти и считывает очередную команду. Такой порядок работы действует только при отсутствии команд условного или безусловного перехода. Если необходимо перейти к новому участку программы, очередь сбрасывается, в ПС заносится соответствующий адрес, ШИ выбирает эту команду и передает ее в ОУ. Пока О У выполняет команду, ШИ заполняет очередь следующими командами.