Бистабильная ячейка.

Информатика

На рис. 3.14, а, б изображены логические схемы бистабильной ячейки, на рис. 3.14, в, г — принципиальные схемы ячейки для двух состояний. Бистабильная ячейка представляет собой два инвертора, включенных по кольцевой схеме, в которой выход первого инвертора подключен к входу второго, а выход второго — к входу первого. Возможны только два устойчивых стационарных состояния бистабильной ячейки, если… Читать ещё >

Бистабильная ячейка. Информатика (реферат, курсовая, диплом, контрольная)

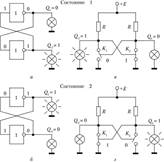

На рис. 3.14, а, б изображены логические схемы бистабильной ячейки, на рис. 3.14, в, г — принципиальные схемы ячейки для двух состояний. Бистабильная ячейка представляет собой два инвертора, включенных по кольцевой схеме, в которой выход первого инвертора подключен к входу второго, а выход второго — к входу первого. Возможны только два устойчивых стационарных состояния бистабильной ячейки, если на выходе первого инвертора Q, = 0, на выходе второго — Q2 = 1 (рис. 3.14, а, в) или на выходе первого инвертора Q, = 1, на выходе второго — Q2 = 0 (рис. 3.14, б, г).

Состояния Qj = Q2 = 0 и Qt = Q2 = 1 невозможны, поскольку при этих сигналах инверторы не выполняют своих функций. Такие состояния являются неустойчивыми и после их появления бистабильная ячейка должна перейти в одно из устойчивых состояний. Например, при Q1 = Q2 = 0.

Рис. 3.14. Бистабильная ячейка: состояния логической (а, б) и принципиальной (в, г) схем.

после подачи напряжения +Е ячейка принимает одно из устойчивых состояний.

Бистабильная ячейка обладает способностью хранить 1 бит данных в течение всего времени, пока на нее подается напряжение +Е, и поэтому служит основой для построения триггеров.

Асинхронный RS-триггер на элементах ИЛИ-НЕ

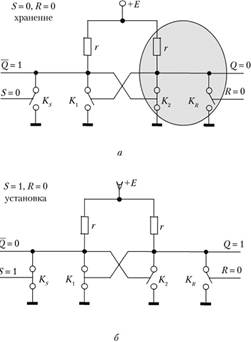

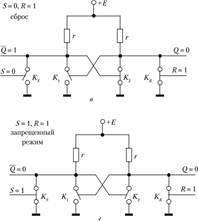

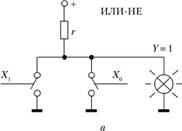

Для построения триггера необходимо в бистабильную ячейку ввести два ключа (транзистора), чтобы управлять ее состоянием. Подключив управляемые ключи Ks и KR параллельно ключам К{ и К2 бистабильной ячейки, получим принципиальную схему асинхронного RS-триггера на двух логических элементах ИЛИ-HE (рис. 3.15, а). В этом нетрудно убедится, если рассмотреть выделенный овалом фрагмент схемы на рис. 3.15, а и составить для него таблицу истинности (рис. 3.16).

Рис. 3.15. Режимы или состояния RS-триггера на элементах ИЛИ-HE.

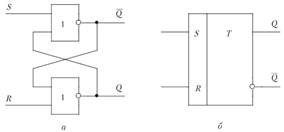

На рис. 3.17, а приведена логическая схема асинхронного RS-триггера, а на рис. 3.17, б — его условное графическое обозначение.

Принцип работы. Асинхронный RS-триггер имеет два информационных входа: S (Set — установка) для установки 1 и R (Reset — сброс) для установки 0 и два выхода: прямой Q и инверсный Q. Состояние триггера характеризуется сигналом на выходе Q и определяется комбинацией сигналов S и R. Для пояснения принципа работы триггера положим, что Sk, Rk, Qk — значения сигналов на k-м временно? м интервале; Q* 1 — предшествующее состояние триггера. Выявим состояния триггера (значения выходного.

Рис. 3.16. Принципиальная схема (а) и таблица истинности (б) элемента ИЛИ-НЕ.

сигнала Q*) для двух предшествующих состояний ((У' -1 = 0 и Qk~ 1 = 1) после подачи на его вход четырех возможных комбинаций входных сигналов Sk, Rk (00, 01,10 и 11).

Рис. 3.17. Логическая схема (а) и условное графическое обозначение (б) асинхронного триггера на элементах ИЛИ-НЕ.

- 1. Если на входы триггера подать нулевые сигналы Sk = Rk = 0, то ключи Кр KR будут заперты и состояние триггера не изменится, т. е. Q* = Q*~1. Нулевые сигналы на обоих входах соответствуют состоянию (режиму) хранения.

- 2. При подаче на входы триггера сигналов 5* = 1, = 0 (см. рис. 3.15, б) ключ Ks замыкается, а ключ KR размыкается, поэтому происходит установка триггера в состояние Q* = 1 независимо от предыдущего состояния Q* 1 (режим установки).

- 3. После подачи входных сигналов Sk = 0, Rk = 1 (см. рис. 3.15, в) ключ Ks размыкается, а ключ KR замыкается, и триггер независимо от предыдущего состояния <2* «1 переходит в состояние Q* = 0 (режим сброса).

- 4. После подачи сигналов Sk = Rk = 1 ключи Ks, KR будут замкнуты, что соответствует Qk = Qk 0 независимо от предыдущего состояния триггера Qj1 ~ ', а ключи KVK2 - разомкнуты (см. рис. 3.15, г). Если теперь перейти в режим хранения, подав на входы триггеров сигналы Sk = Rk = 0, то ключи Ку KR разомкнутся. Их можно изъять из схемы. В оставшейся бистабильной ячейке оба ключа К{ и К2 находятся в одинаковом (разомкнутом) состоянии, при котором Qk =Qk 0.41 таком (неустойчивом) состоянии ячейка находиться не может, она должна перейти в одно из двух возможных устойчивых состояний. В какое состояние она перейдет — неизвестно, т. е. состояние триггера окажется неопределенным. Поэтому комбинация входных сигналов Sk = Rk = 1 является запрещенной (запрещенный режим).