Мажоритарным элементом (majority logic gate) называют пороговое устройство с нечетным числом входов М, выходной сигнал У которого равен 1 только при поступлении на его входы не менее К = (М + 1)/2 входных сигналов Хт = 1 (т = 0, 1,2, 1) [60, 72].

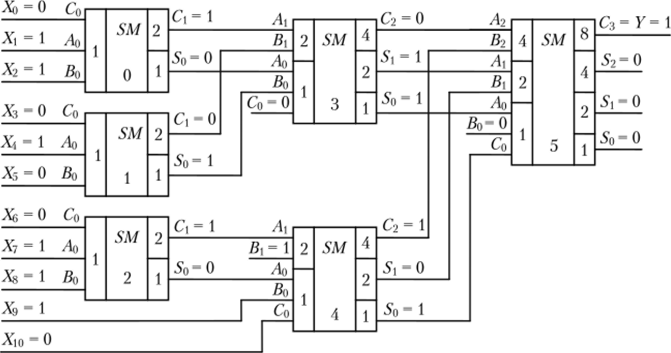

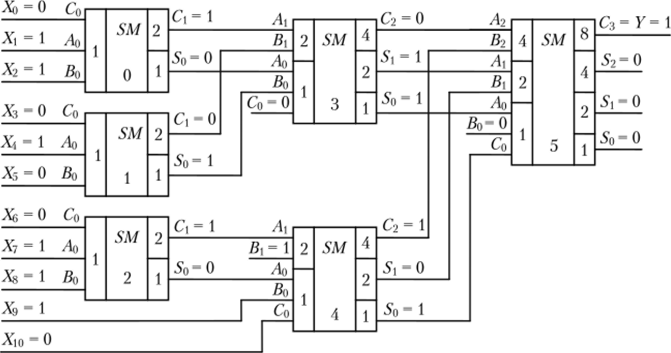

На рис. 9.103 приведена схема 11-входового мажоритарного элемента, содержащего три одноразрядных сумматора в первом ярусе, два двухразрядных сумматора во втором ярусе и один трехразрядный сумматор в третьем ярусе.

Отличием мажоритарного элемента от рассмотренного выше порогового устройства является то, что при минимальном числе логических единиц в комбинации входных сигналов, равном 6, на выходах сумматора SM-5 третьего яруса формируется двоичное число C3S2SXS0 = 0110. Для смещения порога К до уровня 23 = 10002 на вход сумматора SM-4 подан сигнал В, = 1 с весом 2' = 2 (можно подать С0 = 1 на вход SM-3 и В0 = 1 на вход SM-5). Принятая мера позволяет в качестве выхода У мажоритарного элемента выбрать выход переноса С3 сумматора SM-5, на котором при числе единиц в комбинации входных сигналов, равном или больше шести, устанавливается уровень логической единицы. Свободные входы ?"сумматора SM-3 и В" сумматора SM-5 подключаются к общей точке схемы, что соответствует логическому уровню нуля. На рис. 9.103 показа;

Рис. 9.103. Схема 11-входового мажоритарного элемента на сумматорах.

но прохождение комбинации входных сигналов, содержащих шесть единиц, на выход мажоритарного элемента.

Следует отметить, что свободные входы с весом 1 можно использовать для повышения общего числа входов А/ пороговых и мажоритарных устройств. Например, использование входа С0 сумматора 5М-2 порогового устройства 4 из 6 (см. рис. 9.102) позволяет получить семивходовый мажоритарный элемент. Если задействовать входы С0сумматора 5М-3 и В0 сумматора 5А/-5 (см. рис. 9.103), то число входов увеличится до 13. Получим пороговое устройство 6 из 13 (при В{ = 1 в 5М-4) и 8 из 13 (при В, = 0 в 5М-4).

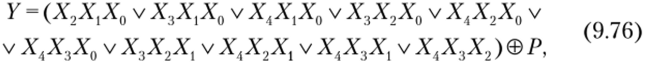

В интегральном исполнении выпускаются 3- и 5-входовые мажоритарные элементы. Выходной сигнал 5-входового мажоритарного элемента описывается следующим выражением [60]:

где Р (ро1агку) — управляющий сигнал для инвертирования выходного сигнала У мажоритарного элемента.

Подстановкой в соотношения (9.76) определенных значений сигналов можно получить описание элементов с различными функциями:

- • при Х4 = 1,Х3 = 0 получаем выражение У = (Х^С{ VХ^чХ{Х0)®Р для 3-входового мажоритарного элемента с возможностью инвертирования выходного сигнала;

- • при Х4 = Х3 = 0 выходной сигнал У = Х2Х{Х0 © Р соответствует З-входовому логическому элементу И/И-ЫЕ;

- • при Х4 = Х3 = 1 выходной сигнал У = Х2 V X, V Х0 © Р соответствует З-входовому логическому элементу ИЛИ/ИЛИ-НЕ.