Структура адресных ЗУ

Структура 2 DM используется не только для ЗУ типа ROM, но и для ЗУ типа RAM с операциями чтения и записи. В этих ЗУ вместо мультиплексоров используются управляемые буферы данных, выполняющие не только функции мультиплексирования и выдачи данных в шину DO, но и функции приема данных по шине DI и формирования сигналов записи для соответствующих ЗЭ. Направление передачи данных определяется сигналом… Читать ещё >

Структура адресных ЗУ (реферат, курсовая, диплом, контрольная)

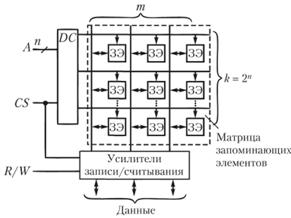

В полупроводниковых ЗУ адресного типа можно выделить две основные функциональные части: матрицу запоминающих элементов, обеспечивающую хранение данных, и схему выборки, обеспечивающую запись или считывание информации в выбранной ячейке памяти (рис. 4.2). Матрица ЗЭ — прямоугольная и в ранних образцах ЗУ имела размерность М = k • т, где М — информационная емкость памяти в битах; k — число хранимых слов; т — их разрядность. Схема выборки состоит из дешифратора адресного кода DC и усилителей записи/считывания.

Рис. 4.2. Структура ЗУ типа 2D

Каждая строка матрицы ЗЭ соответствует ячейке памяти и хранит одно слово данных, а номера строк соответствуют адресам ячеек. Адрес выбранной ячейки по шине адреса поступает на все микросхемы памяти, но воспринимается только той микросхемой, на которую пришел разрешающий сигнал CS (Chip Select — выбор кристалла). С приходом сигнала CS дешифратор адресного кода активизирует одну из выходных линий, разрешая одновременный доступ ко всем элементам выбранной строки. Одноименные разряды всех ячеек образуют столбцы матрицы, соединяемые вертикальными линиями — внутренними линиями данных. Если осуществляется операция чтения, то состояния ЗЭ выбранной строки транслируются по этим линиям, усиливаются и выдаются на внешнюю шину данных. Если же выполняется операция записи, то усилители устанавливают на линиях уровни напряжения в соответствии с записываемыми данными, и ЗЭ переходят в соответствующие состояния «пуля» или «единицы». Подобная структура ЗУ получила название структуры 2D.

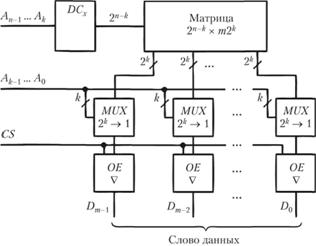

Структура 2D может быть использована только в ЗУ малой информационной емкости. С ростом емкости возрастает сложность дешифратора, поскольку число его выходных линий равно числу хранимых слов. Для ЗУ большой информационной емкости структура была усовершенствована, она получила название структуры 2DM. На рис. 4.3 показана такая структура для ЗУ типа ROM. В ней возбужденный выход дешифратора DCX по-прежнему выбирает целую строку матрицы ЗЭ. Однако, в отличие от предыдущей структуры, длина строки не равна разрядности хранимых слов, а многократно ее превышает. Число строк матрицы, а значит, и число выходов дешифратора теперь меньше количества хранимых слов. Для выбора одной из строк служат не все разряды адресного кода, а их часть Аn-1,…, Ак. Остальные разряды адреса (от Ак-1, до А0) используются для того, чтобы выбрать необходимое слово из множества слов, содержащихся в этой строке. Это выполняется с помощью мультиплексоров, на адресные входы которых подаются коды Ак_1, …, А0. Длина строки равна т2к, где т — разрядность хранимых слов. Каждый отрезок строки длиной 2к хранит все одноименные (нулевые, первые, …, т-e) разряды всех 2к слов этой строки. Из каждого такого отрезка мультиплексор выбирает один бит. Количество мультиплексоров соответствует количеству разрядов в слове. Таким образом, на выходах мультиплексоров формируется выходное слово. По разрешению сигнала CS, поступающего на входы ОЕ управляемых буферов с тремя состояниями, выходное слово передается на внешнюю шину.

Рис. 4.3. Структура ЗУ типа 2DM

Структура 2DM используется не только для ЗУ типа ROM, но и для ЗУ типа RAM с операциями чтения и записи. В этих ЗУ вместо мультиплексоров используются управляемые буферы данных, выполняющие не только функции мультиплексирования и выдачи данных в шину DO, но и функции приема данных по шине DI и формирования сигналов записи для соответствующих ЗЭ. Направление передачи данных определяется сигналом R/W, а управление буферами данных осуществляется дешифратором.