Функциональная схема.

Устройство умножения восьмиразрядное

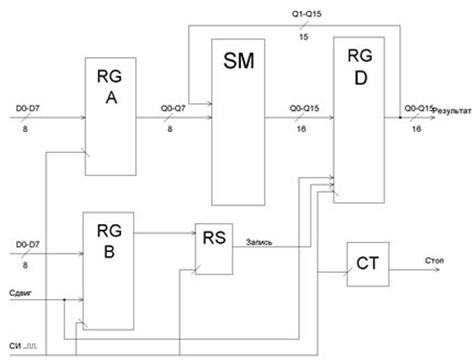

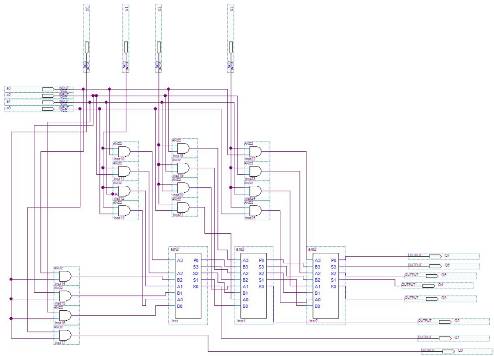

Функциональная схема цифрового устройства может быть разбита на иерархические уровни, простейшим из которых является уровень логических элементов, которые служат базой для проектирования более сложных устройств. Именно поэтому исследование параметров элементной базы является важным для дальнейшего проектирования и корректного функционирования разработанного устройства (рисунок 8). Схема образует… Читать ещё >

Функциональная схема. Устройство умножения восьмиразрядное (реферат, курсовая, диплом, контрольная)

Функциональная схема цифрового устройства может быть разбита на иерархические уровни, простейшим из которых является уровень логических элементов, которые служат базой для проектирования более сложных устройств. Именно поэтому исследование параметров элементной базы является важным для дальнейшего проектирования и корректного функционирования разработанного устройства (рисунок 8).

Элементы 1-го уровня иерархии:

- -2И, 2ИЛИ, НЕ, 2XOR, 3И-НЕ, 2И-НЕ;

- — элементы 2-го уровня иерархии:

- — триггеры RS, D; JK, T;

- — сумматоры;

- — мультиплексоры.

Рисунок 8 — Функциональная схема устройства

Описание проекта на языке VHDL и Verilog

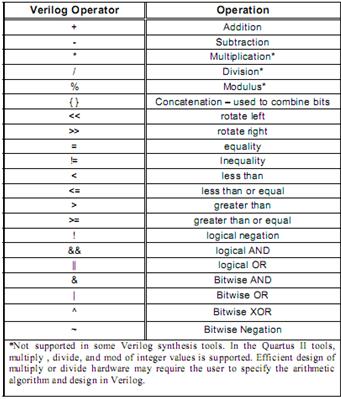

Описание элемента умножение на языке Verilog в Приложении A.

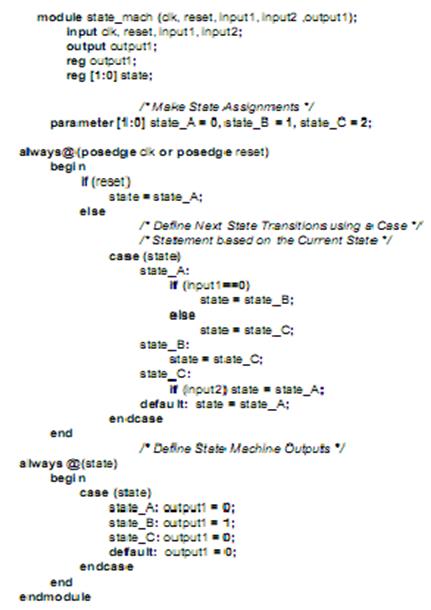

Операторы языка Verilog на рисунке 9.

Рисунок 9 — Язык Verilog.

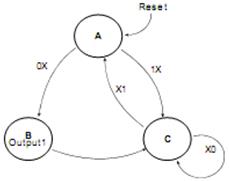

Реализации конечного автомата и его диаграмма состояний на рисунке 10 и 11.

Рисунок 10 — Схема автомата.

Рисунок 11- Verilogконечный автомат.

Работа электрической схемы

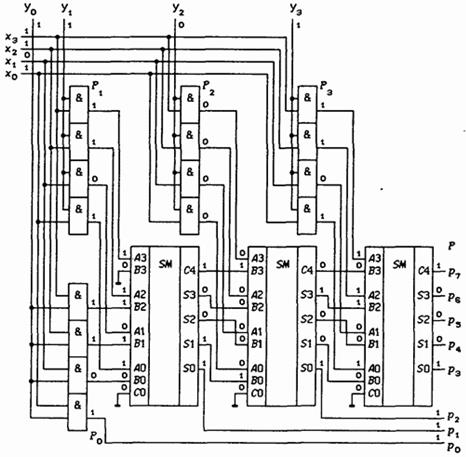

Структурная электрическая схема устройства умножения четырехразрядных двоичных чисел представлена на рисунке 11.

Умножитель Y3 предназначен для умножения четырехразрядных двоичных чисел A и B, представленных разрядами, ,, и, ,,. На выходе умножителя формируется восьмиразрядное произведение Q, представленное разрядами ,…,.

Регистр Y1 предназначен для параллельного ввода четырехразрядного множимого A в двоичной системе счисления (СС). Значение множимого A может меняться в пределах от 0 до 15 в десятичной СС.

Счетчик Y2 предназначен для параллельного ввода четырехразрядного множителя B в двоичной СС. Значение множителя B также может меняться от 0 до15 в десятичной СС.

Регистр Y4 предназначен для параллельного вывода результата умножения, который представляет собой восьмиразрядное кодовое слово.

Загрузка сомножителей и запись результата умножения синхронизируется тактовыми импульсами. Причем ввод сомножителей осуществляется по отрицательным фронтам тактовых импульсов, а вывод результата умножения — по положительным.

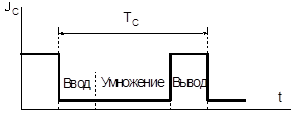

Процесс функционирования устройства поясняется временной диаграммой, которая представлена на рисунке 12.

Рисунок 12 — Временная диаграмма, поясняющая процесс функционирования устройства.

В момент времени по отрицательному фронту тактового импульса начинается ввод сомножителей в регистр Y1 и счетчик Y2 (рисунок 9). К моменту времени ввод заканчивается, и начинается процесс умножения в умножителе Y3. Этот процесс в худшем случае завершается к моменту времени. Затем по положительному фронту тактового импульса результат умножения записывается в регистр Y4 и т. д. При подаче низкого уровня напряжения на вход (рисунок 9) устройство сбрасывается в исходное нулевое состояние. Один из вариантов структурной схемы умножителя для m = n = 4 показан на рисунке 13.

Рисунок 13- Умножитель четырехразрядных двоичных чисел.

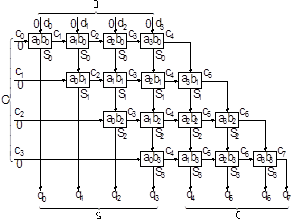

Матричное умножение на рисунке 14.

Схема образует матрицу, сформированную проводниками, по которым передаются разряды числа A и числа B. В точках пересечения этих проводников находятся логические элементы «2И». Именно по этой причине умножители, реализованные по данной схеме, получили название матричных умножителей. Такая схема представлена в QuartusIIна рисунке 15.

Рисунок 14 — Схема матричного умножителя 4*4.

Рисунок 15- Схема матричного умножителя в Quartus II.