Режимы работы контроллера ПДП

Рис. 5.37. Схема связи КПДП фирмы Intel с системной шиной, ЦП и ВУ Выводы DB7—DB0 — линии данных двунаправленные. В программном режиме работы линии DB7—DB0 служат для приема управляющей информации от процессора или для передачи статусной информации в процессор, но линиям ШД D7—D0. В режиме ПДП на выводы DB7—DB0 контроллер ПДП выдает восемь разрядов адреса ОЗУ, которые необходимо защелкнуть… Читать ещё >

Режимы работы контроллера ПДП (реферат, курсовая, диплом, контрольная)

Каждый КПДП может быть запрограммирован для обслуживания запросов:

- • с фиксированными приоритетами каналов;

- • с циклическим изменением приоритетов каналов.

При фиксированных приоритетах, паивысший приоритет устанавливается за каналом с меньшим номером DREQ0. При циклическом изменении приоритетов каналов, самый низкий приоритет присваивается каналу после его обслуживания (аналогично ПКП). Это позволяет обслужить все каналы поочередно. Имеется возможность автоматической инициализации каналов КПДП, т. е. повторения циклов ПДП с единожды установленными параметрами, без перепрограммирования. Наряду с обслуживанием ВУ КПДП позволяет реализовать передачу «память — память».

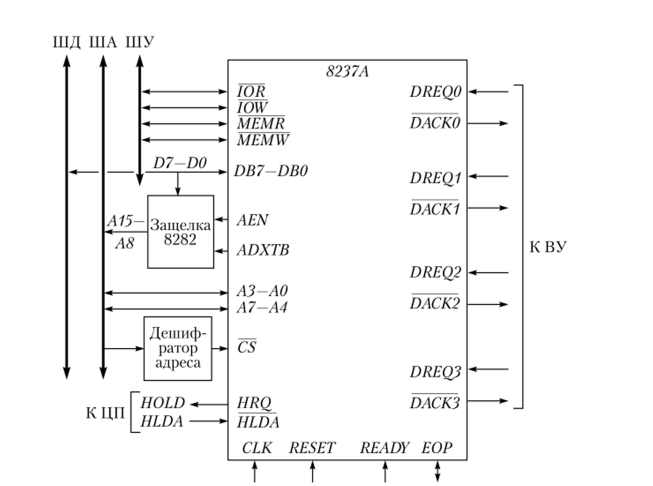

Схема связи КПДП с внешним устройством, центральным процессором, системной шиной и назначение выводов большой интегральной схемы.

Назначение выводов связи БНС КПДП с системной шиной ЭВМ меняется в зависимости от режима его работы (программный или ПДП) (рис. 5.37).

Рис. 5.37. Схема связи КПДП фирмы Intel с системной шиной, ЦП и ВУ Выводы DB7—DB0 — линии данных двунаправленные. В программном режиме работы линии DB7—DB0 служат для приема управляющей информации от процессора или для передачи статусной информации в процессор, но линиям ШД D7—D0. В режиме ПДП на выводы DB7—DB0 контроллер ПДП выдает восемь разрядов адреса ОЗУ, которые необходимо защелкнуть во внешнем регистре-защелке (Intel 8282). Выходы регистра-защелки подключаются к адресным линиям А15—А8 магистрали ЭВМ. В режиме ПДП контроллер не управляет ШД, соответствующие выводы шины данных DB7—DB0 контроллера свободны. Выводы АЗ—АО — адресные входывыходы. В программном режиме работы КПДП выводы АЗ—АО используются как входы для адресации регистров КПДП.

Контроллер прямого доступа к памяти в программном режиме использует 16 адресов в адресном пространстве ввода-вывода. В режиме ПДП выводы АЗ—АО используются как выходы, но ним передаются четыре младших разряда адреса ОЗУ, которые выводятся на адресные линии АЗ—АО магистрали ЭВМ.

Выводы А7—А4 — адресные выходы. В программном режиме работы КПДП выводы А7—А4 не используются, переходят в высокоимнедансное состояние. В режиме ПДП контроллер на выводы А 7—А4 передает соответствующие разряды адреса ОЗУ.

Таким образом, в режиме ПДП контроллер выдает на ША только 16 разрядов адреса. Но в режиме ПДП при работе с памятью ЭВМ контроллер должен использовать как минимум 24-разрядные адреса памяти. Младшие 16 бит адреса выводятся контроллером на шину адреса ЭВМ. Старшие биты адреса контроллер не выдает, и их необходимо программировать до начала передачи ПДП.

Для хранения старших бит адреса используется специальный регистр страниц (табл. 5.6). В программном режиме работы КПДП в регистр страниц можно вывести данные, как в любой порт. Во время передачи по каналу ПДП содержимое регистра страниц изменять нельзя. Следовательно, за одну передачу можно передать максимум 2Ш = 65 536 байт, так как КПДП может менять адрес в пределах младших 16 разрядов.

Таблица 5.6.

Назначение каналов КПДП и адреса регистров страниц.

Номер КПДП. | Номер канала. | Назначение канала. | Адрес регистра страниц. |

Резерв (регенерация ОЗУ). | 87h | ||

Резерв. | 83h КАМАК. Sound. | ||

НГМД. | 81 h | ||

Резерв. | 82h | ||

Каскадирование. | |||

Резерв. | 8Bh Sound. | ||

То же. | 8% | ||

-//; | 8Ah |

Из регистра страниц данные выводятся на линии А16—А23 ША. Вывод -'CS — выбор кристалла — связан с ША посредством дешифратора адреса и определяет базовый адрес КПДП в адресном пространстве ввода-вывода ЭВМ. В программном режиме работы с ЦП вывод -?CS используется как вход, разрешает связь КПДП с системной шиной (если «О») или запрещает (если «1»), В режиме ПДП -?CS не используется, переходя в высокоимпеданснос состояние.

В программном режиме базовые адреса регистров контроллеров, в области адресов ввода-вывода соответственно равны:

- • 1-й КПДП Oh (0. Fh)

- • 2-й КПДП COh (COh. DFh).

Выводы ^MEMR/^MEMW — чтение/запись в программном режиме работы не используются, переходя в высокоимпедансное состояние. В режиме ПДП выводы ~'MEMR/~'MEMW используются как выходы, определяют направление передачи данных по отношению к ОЗУ.

Выводы -'IORf-'IOW — вывод/ввод в программном режиме работы используются как входы для чтения {-'IOR = 0) или записи (->IOW = 0) регистров контроллера. Выводы -?IORf-'IOWв режиме ПДП используются как выходы, указывают ВУ, установившему запрос ПДП, направление передачи данных по отношению к ВУ: или из регистров данных интерфейса (->IOR = 0), или в регистры данных интерфейса (~'IOW= 0).

Вывод AEN (address enable) — разрешение адреса, в режиме ПДП показывает, что на ШД установлен адрес. В программном режиме работы вывод AENпереходит в высокоимпедансное состояние. В режиме ПДП вывод AEN используется как выход. Вывод АДА’устанавливается в «1» (AEN =1) на время выдачи восьми старших разрядов адреса ОЗУ на линии DB7—DB0.

Вывод AD ST В (address strobe) — строб адреса. В программном режиме работы переходит в высокоимпедансное состояние. В режиме ПДП ADSTB используется как выход. На нем формируется импульс (строб), осуществляющий запись старших разрядов адреса ОЗУ (А15—А8) с линий DB7—DB0 в регистр-защелку.

Вывод HRQ (hold request) — запрос шины (выход). В режиме ПДП используется для формирования требования к ЦП (по линии HOLD) передать управление системной магистралью КПДП.

Вывод HLDA (hold acknowledge) — подтверждение шины (вход). Центральный процессор использует вывод HLDA для сообщения контроллеру ПДП о возможности выполнения циклов ПДП.

Вывод CLK — синхронизация служит для подключения тактового генератора Folk = 3 МГц.

Вывод RESET — сброс переводит контроллер в исходное состояние и маскирует все запросы ПДП от внешних устройств.

Вывод READY — готовность. В программном режиме работы переходит в высокоимпедансное состояние. В режиме ПДП может использоваться (как вход) для синхронизации работы контроллера ПДП с медленно действующими устройствами. Низкий уровень на входе READY, установленный ВУ, задерживает цикл ПДП.

Вывод -?ЕОР — окончание процесса. В режиме ПДП КПДП формирует на линии ЕОР импульс при достижении счетчиком циклов ПДП конечного значения (-1), который может служить запросом прерывания и подается в интерфейс ВУ для установки признаков завершения обмена. Интерфейс ВУ может выдать на эту линию сигнал с активным уровнем (0), который свидетельствует о невозможности устройства продолжать обмен данными. В любом случае активный уровень сигнала на линии ЕОР = 0 завершает передачу ПДП.

Выводы DREQ0—DREQ3 — входы запросов ПДП от внешних устройств. В исходном состоянии DREQ0 имеет наивысший приоритет, DREQ3 — низший.

Выводы DACK0—DACK3 — выходы сигналов подтверждения ПДП. Используются для сообщений ВУ о возможности выполнения циклов ПДП. Полярность сигналов запросов и подтверждения задается программно. После сигнала RESET на выводах DACK устанавливается пассивный уровень.