Аналого-цифровые преобразователи.

Системы автоматического управления высшей точности

АЦП поразрядного уравновешивания по принципу действия аналогичен взвешиванию с помощью гирь. В регистр последовательно, начиная со старшего разряда, заносятся единицы, и если получаемый выходной сигнал ЦАП остается меньше входного сигнала АЦП, единица сохраняется, иначе заменяется нулем. Количество операций сравнения задано количеством разрядов, время преобразования не зависит от входного… Читать ещё >

Аналого-цифровые преобразователи. Системы автоматического управления высшей точности (реферат, курсовая, диплом, контрольная)

Аналого-цифровые преобразователи (АЦП) применяются для преобразования аналоговых сигналов в цифровые отсчеты для последующей обработки. Остановимся только на важнейших особенностях их применения в САУВТ.

Основные характеристики АЦП: разрешающая способность, точность и быстродействие.

Разрешающая способность определяется разрядностью и максимальным диапазоном входного аналогового напряжения (полной шкалой). Также ее можно исчислить как отношение максимального входного напряжения к напряжению, соответствующему единице младшего разряда.

Точность определяется абсолютной погрешностью шкалы 5П ш, нелинейностью 8Л, дифференциальной нелинейностью 8Л диф.

Быстродействие АЦП характеризуется временем преобразования *прб> т-е— интервалом времени от момента заданного изменения сигнала на входе до появления на выходе установившегося кода.

Классификация АЦП по структуре построения: выделяют АЦП с применением ЦАП и АЦП без ЦАП.

К первому типу относятся: а) АЦП развертывающего типа (последовательного счета); б) следящие АЦП с ЦАП в обратной связи; в) АЦП поразрядного уравновешения; г) АЦП параллельного преобразования.

Ко второму типу относятся АЦП двойного интегрирования, АЦП параллельного действия и АЦП с ХД-модуляцией (следящие без ЦАП с преобразованием на основе принципа широтно-импульсной модуляции) [16—23].

В АЦП развертывающего типа формируется линейно нарастающее напряжение с помощью ЦАП на выходе счетчика с генератором на входе. Момент совпадения значений нарастающего сигнала с входным сигналом фиксируется пороговым устройством, после чего в качестве результата операции преобразования на выход поступает цифровой код счетчика. Достоинство таких АЦП — простота реализации, недостатки — зависимость длительности преобразования от величины входного сигнала, низкая помехозащищенность.

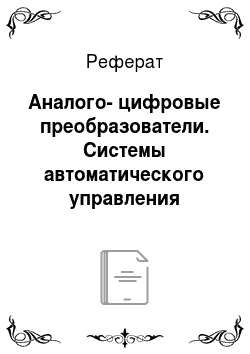

Следящий АЦП может быть сделан на основе аналогичного соединений счетчика и ЦАП, если счетчик сделать реверсивным, а напряжение с выхода ЦАП вычесть из входного напряжения и знак получающейся при этом величины сигнала ошибки использовать для управления направлением счета счетчика, как показано на рис. 5.23. В таком АЦП напряжение на выходе ЦАП будет повторять низкочастотную составляющую входного сигнала, но при этом возможны периодические колебания на несколько единиц младшего разряда около среднего текущего значения. Достоинство такого метода (простота) может раскрыться лишь при преобразовании медленно меняющихся сигналов; при быстрых или скачкообразных изменениях этот способ неэффективен.

АЦП поразрядного уравновешивания по принципу действия аналогичен взвешиванию с помощью гирь. В регистр последовательно, начиная со старшего разряда, заносятся единицы, и если получаемый выходной сигнал ЦАП остается меньше входного сигнала АЦП, единица сохраняется, иначе заменяется нулем. Количество операций сравнения задано количеством разрядов, время преобразования не зависит от входного сигнала. Для такого АЦП необходимо, чтобы входной сигнал не изменялся в течение всей операции преобразования (на величину, превышающую вес младшего разряда). Применение УВХ на входе такого АЦП решает эту проблему, но независимо от этого необходим и ФНЧ, устраняющий все частоты, превышающие половину максимальной частоты получения отсчетов (согласно теореме Котельникова). Правильно рассчитанный фильтр должен исключать компоненты сигнала, превышающие по амплитуде половину младшего разряда, а по частоте — половину частоты преобразования. В этом случае применение УВХ практически утрачивает смысл.

АЦП параллельного действия (прямого преобразования) содержат несколько пороговых устройств, с которыми одновременно сравнивается входной сигнал. Результат работы всех компараторов преобразуется и выдается на выход в виде кода. Так строятся самые быстрые АЦП малой разрядности. Увеличение разрядности требует увеличения аппаратных затрат по степенному закону.

Рис. 5.23. Упрощенная схема следящего АЦП.

АЦП с совмещением поразрядного уравновешивания и параллельного действия позволяет делать АЦП, в которых поразрядное кодирование осуществляется группами по 2—4 разряда. По этому принципу построено большинство прецизионных АЦП.

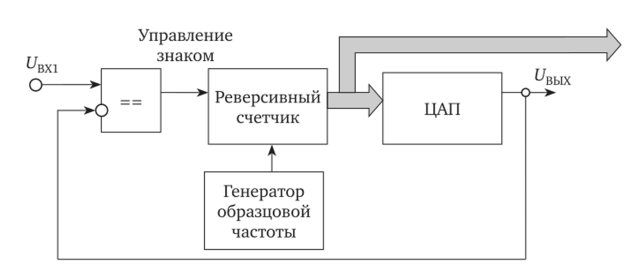

АЦП двойного интегрирования (например, К572ПВ2) содержит преобразователь величины входного напряжения в заряд (путем заряда емкости через формирователь тока, как это делается в УВХ) и преобразователь заряда в длительность (на основе интегратора), как показано на рис. 5.24.

Рис. 5.24. Упрощенная схема АЦП двойного интегрирования.

На первом такте конденсатор С] заряжается через ключ SW). Величина заряда зависит от величины входного сигнала. На втором этапе этот конденсатор Сх разряжается через ключ SW2. Время разряда подсчитывается счетчиком и трактуется как цифровой отсчет значения аналогового сигнала. Логическое устройство управляет работой ключей и счетчика. Разрешение счетчика может существенно превышать точность формирования импульсов эталонной и измеряемой длительностей, несмотря на имеющиеся схемы калибровки, поэтому погрешность такого АЦП может составлять несколько процентов, тогда как по признаку разрядности она должна быть на уровне долей процента. АЦП двойного интегрирования дешевы и хорошо подавляют сетевые и ВЧ-помехи, часто содержат встроенные преобразователи в код управления знаковым индикатором и даже сам индикатор. Они, несмотря на низкую точность и быстродействие, широко применяются в бытовых цифровых измерителях. В них может быть легко реализован двоично-десятичный код без использования дополнительных декодеров.

Разрядность АЦП не всегда соответствует точности. Например, в АЦП двойного интегрирования (см. рис. 5.24) разрядность определяется длительностью сформированного интервала и образцовой частотой. Например, если частоту увеличить в восемь раз, добавится три дополнительных двоичных разряда. Однако если последовательность двух операций, преобразования входного напряжения в заряд и преобразования заряда в длительность, составляет, например, 1%, то никакое повышение разрядности не снизит погрешность операции преобразования напряжения в код до величины, меньшей, чем эта погрешность.

АЦП с ХД-модуляцией основаны на принципах, развивающих идею следящего АЦП. Если последовательность цифровых отсчетов следящего АЦП, взятых через равные промежутки, усреднить по времени, то можно повысить точность операции преобразования, поскольку такая система автоподстройки содержит интегратор (реверсивный счетчик), а значит, статическая ошибка равна нулю. Таким образом, увеличивая время усреднения, можно увеличивать разрядность. На этом принципе основаны АЦП с ХД-модуляцией, причем в роли одноразрядного ЦАП может быть применен ключ с источником опорного напряжения, т. е. ЦАП как таковой отсутствует. Операция усреднения в этом случае осуществляется встроенным цифровым фильтром, превращающим однобитовую последовательность логических нулей и единиц в многоразрядный медленно меняющийся код. Достоинство таких АЦП — высокая помехозащищенность, низкая стоимость, рекордная разрядность. Точность их преобразования зависит от времени усреднения. Иногда это свойство оборачивается дополнительным достоинством, поскольку АЦП выполняет также функции НЧ-фильтра, а значит, не требует УВХ или внешнего ФНЧ на входе. Чрезвычайно упрощенная схема, показанная на рис. 5.25, поясняет принцип действия такого АЦП.

![Упрощенная схема АЦП с ЕД-модуляцией [19—21].](/img/s/8/01/1317501_3.png)

Рис. 5.25. Упрощенная схема АЦП с ЕД-модуляцией [19—21].

Эта схема требует комментария. Во-первых, компаратор — это однобитный АЦП, поэтому последовательно включенные однобитный АЦП и однобитный ЦАП совместно со схемой сравнения сигналов могут быть заменены одним компаратором. Во-вторых, все же «цифровой фильтр» — слишком общее понятие, лучше использовать термин «преобразователь последовательного кода в параллельный». Название данного типа АЦП происходит от символических обозначений операций суммирования и вычитания греческими заглавными буквами сигма и дельта соответственно. При этом на рис. 5.25 вычитающее устройство обозначено буквой сигма, как традиционно обозначается сумматор, тот факт, что этот сумматор осуществляет операцию вычитания, отмечен лишь знаком «минус» на одном из его входов. Это может вызвать путаницу. Это вычитающее устройство осуществляет операцию, которая в названии АЦП отмечена буквой дельта, а буквой сигма отмечается операция накопления, т. е. интегрирования. Эту операцию делает интегратор. С точки зрения понимания названия АЦП более наглядным был бы рис. 5.26, сделанный на основе рисунка из публикации [19].

![Упрощенная схема АЦП с ЕД-модуляцией из [19].](/img/s/8/01/1317501_4.png)

Рис. 5.26. Упрощенная схема АЦП с ЕД-модуляцией из [19].

Рисунок 5.27 более нагляден, поскольку из него достаточно очевидно следует, что сигнал обратной связи изменяется не в произвольные моменты времени, а лишь в момент поступления тактового импульса на вход сдвигового регистра. Вычитатель вычисляет разницу (дельту) между входным сигналом и сигналом обратной связи. Эта разница интегрируется интегратором, т. е. величина выходного напряжения интегратора растет со скоростью, пропорциональной этой разнице.

За счет действия отрицательной обратной связи на выходе интегратора формируется сигнал, среднее значение которого равно входному сигналу. Если этот сигнал больше, срабатывает компаратор, на вход интегратора поступает отрицательный сигнал, выходной сигнал интегратора начинает уменьшаться. Если сигнал меньше входного, компаратор срабатывает в обратную сторону, на вход интегратора начинает поступать положительный сигнал и выходное напряжение интегратора начинает возрастать. Таким образом, напряжение на выходе интегратора совершает небольшие колебания около уровня, который равен входному сигналу. Компаратор сравнивает эту величину с нулевым значением. Результатом сравнения является логическая единица или ноль. Эта величина передается на выход триггера в момент поступления на его тактовый вход тактового импульса.

Действительно, в системе с интегратором средняя ошибка равна нулю. Указанное среднее значение формируется за счет разницы длительностей формируемых положительных и отрицательных импульсов, т. е. эта импульсная последовательность в своей широтно-импульсной модуляции содержит значение, соответствующее входному сигналу. Теперь только остается преобразовать его в параллельный код. Для этого используется преобразователь последовательного кода в параллельный. Принцип такого преобразования можно пояснить примером.

Например, разобьем интервал, на котором осуществляется преобразование, на 216 равных интервалов и определим знак выходного сигнала компаратора на каждом из этих интервалов. Число интервалов, на которых этот знак положительный, выраженное двоичным кодом, будет значением выходного сигнала 16-разрядного АЦП. Если увеличить длительность интервала, можно, соответственно, увеличить разрядность АЦП при условии, что действие системы не прерывается на протяжении преобразования последовательного кода в параллельный.